JITX

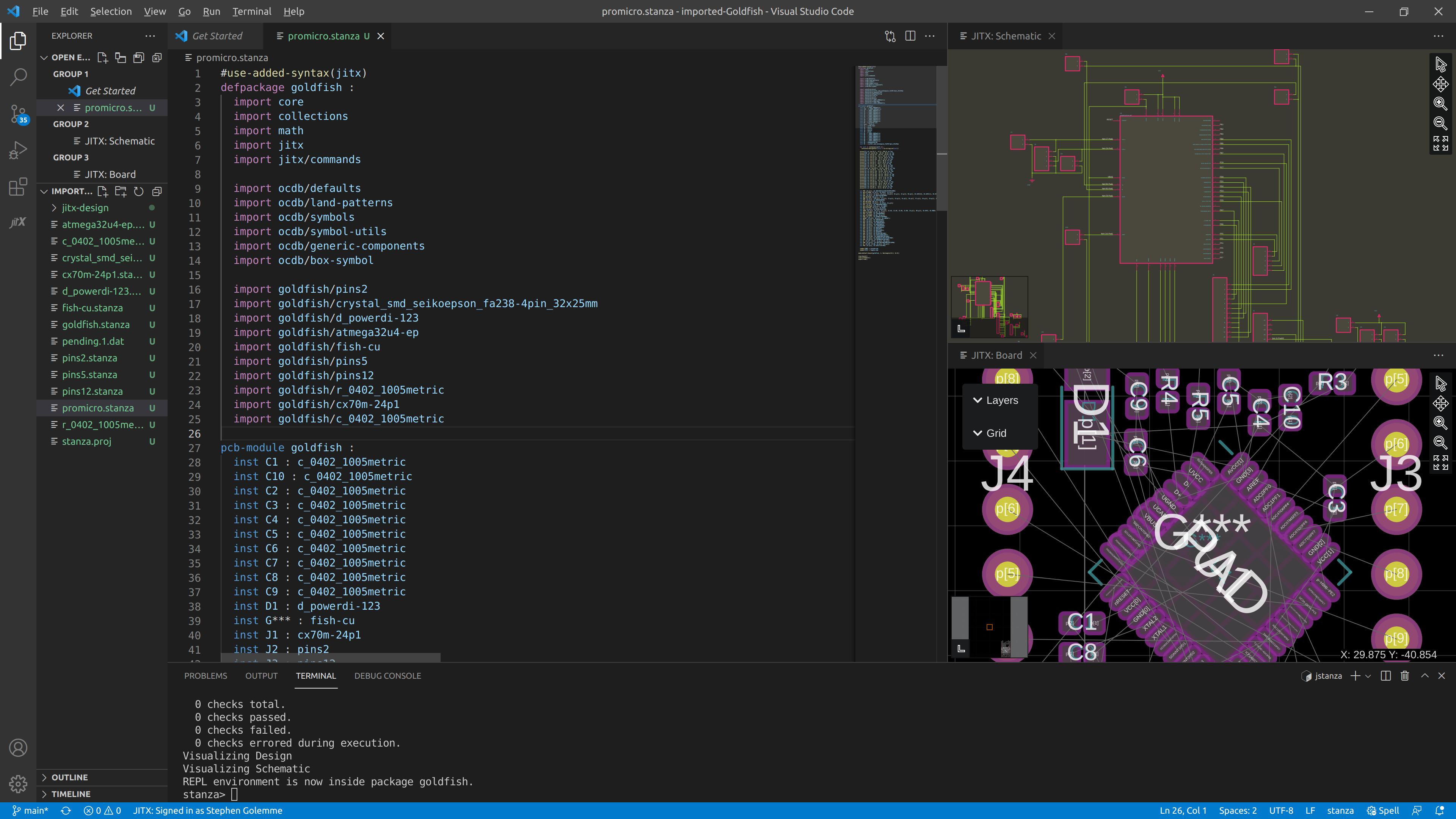

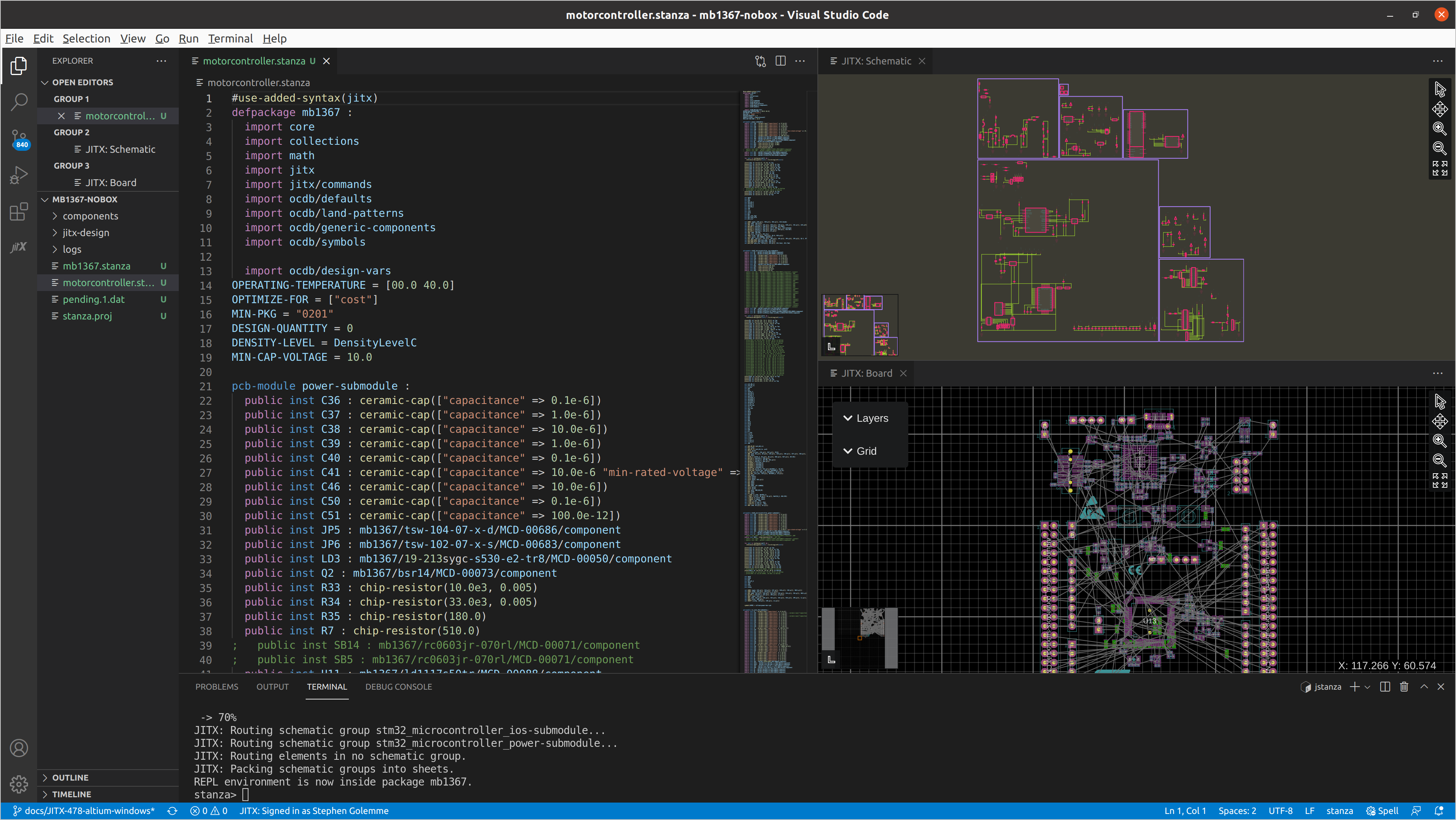

JITX is an EDA tool that lets electrical engineers write code to design circuit boards. With JITX you can write high-level code and use our automation to design circuit boards with super-human speed, correctness and quality.

JITX works on MacOS, Linux, and Windows.

Getting Started

Installing JITX

Instructions for downloading and installing JITX.

Tutorial: Create a circuit

A tutorial covering short topics like how to find components, add them to a design, create nets, and create and use sub-circuits.

Tutorial: Schematic and Layout

A tutorial covering how to style a schematic, and complete a small layout for a power regulator.

Installation Instructions for the JITX App

This page walks you through the steps to install and log in to JITX.

Before using JITX, you must set up your JITX account -- instructions have been sent via email.

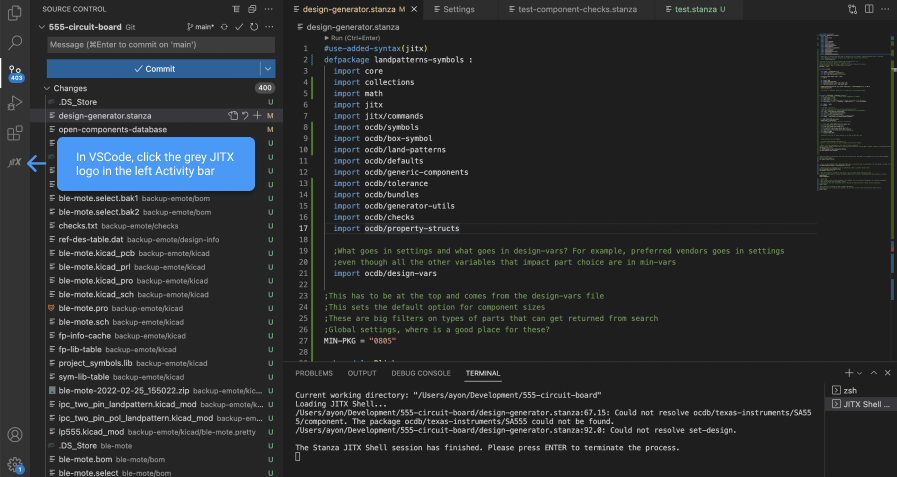

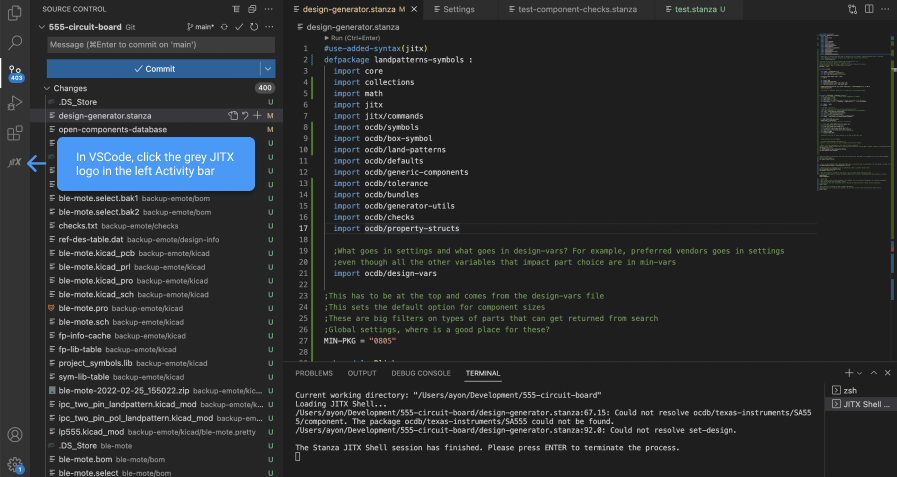

JITX is shipped as an extension for VS Code. Therefore, we first install VS Code and then add the JITX extension for VS Code.

Steps:

1 Install Visual Studio Code

The JITX compiler and UI are integrated with VS Code. VS Code is an integrated development environment (IDE) which integrates tools for development including an editor, compiler, and source control. To install VS Code:

- MacOS

- Linux (For Ubuntu use:

sudo apt-get install code- do not use snap, which installs an old version) - Windows (we can also install from Microsoft store)

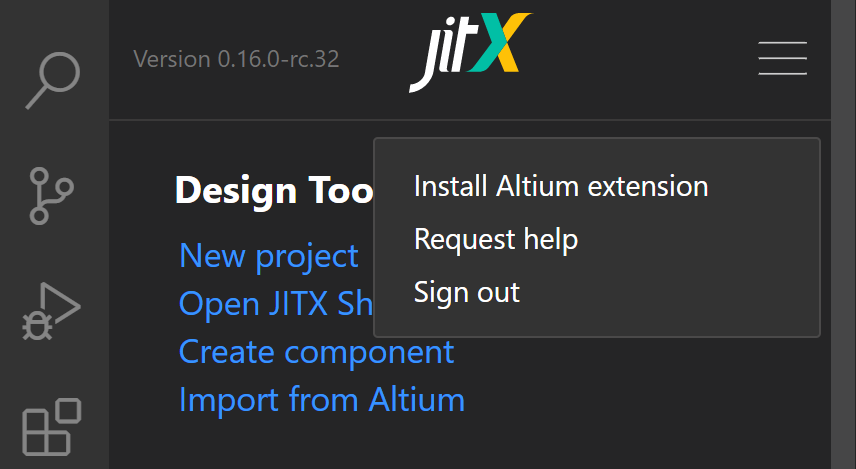

2 Install the JITX VS Code Extension

There are two ways to install the JITX VS Code extension.

Method 1: Install from the Visual Studio Marketplace

Follow the instructions from the marketplace: While in VS Code, Ctrl-P, enter ext install JITX.jitpcb-vscode in the text box and then press Enter to install the JITX VS Code extension directly.

Method 2:

Click the Extensions icon ![]() in the Activity Bar, search for "jitx" and install it.

in the Activity Bar, search for "jitx" and install it.

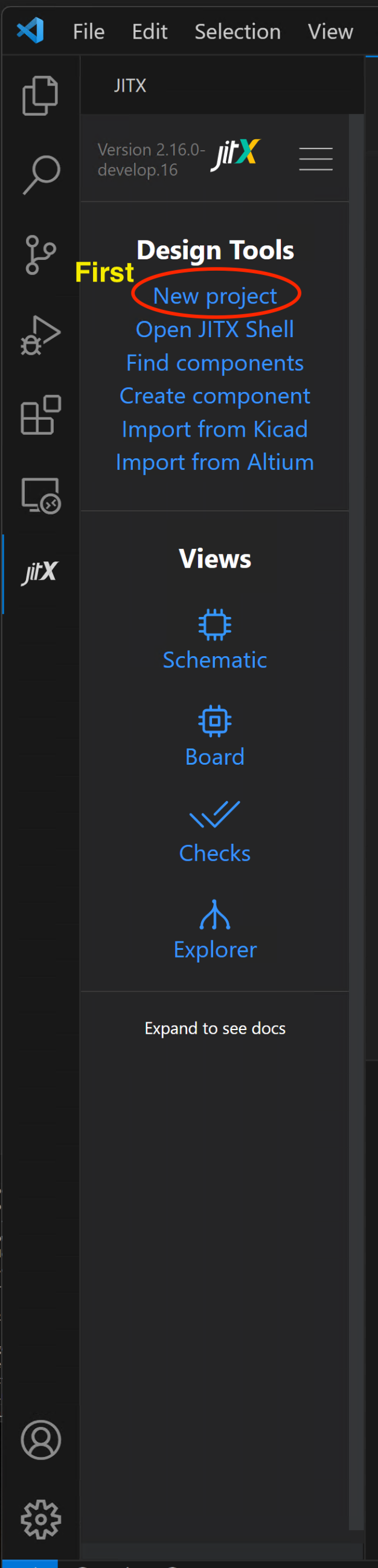

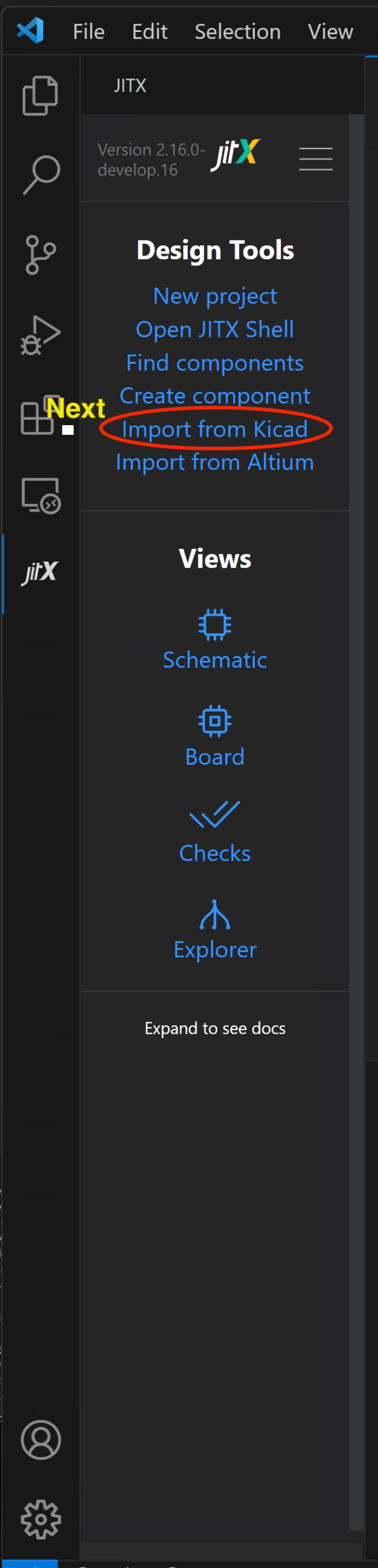

3 Open the sidebar

Click on the JITX icon in the left hand activity bar to open the JITX sidebar.

4 Login to JITX

Click the JITX icon ![]() in the Activity Bar and sign in with the username and password you created using the link from the welcome email.

in the Activity Bar and sign in with the username and password you created using the link from the welcome email.

That's it! You're ready to start designing circuit boards in JITX. Next section: Your first JITX design

Tutorial: Create a circuit

NOTE: Before starting this tutorial, you should have installed and set up JITX.

You can follow along with this tutorial in the video above. Below is a transcript to make the code and text easier to read.

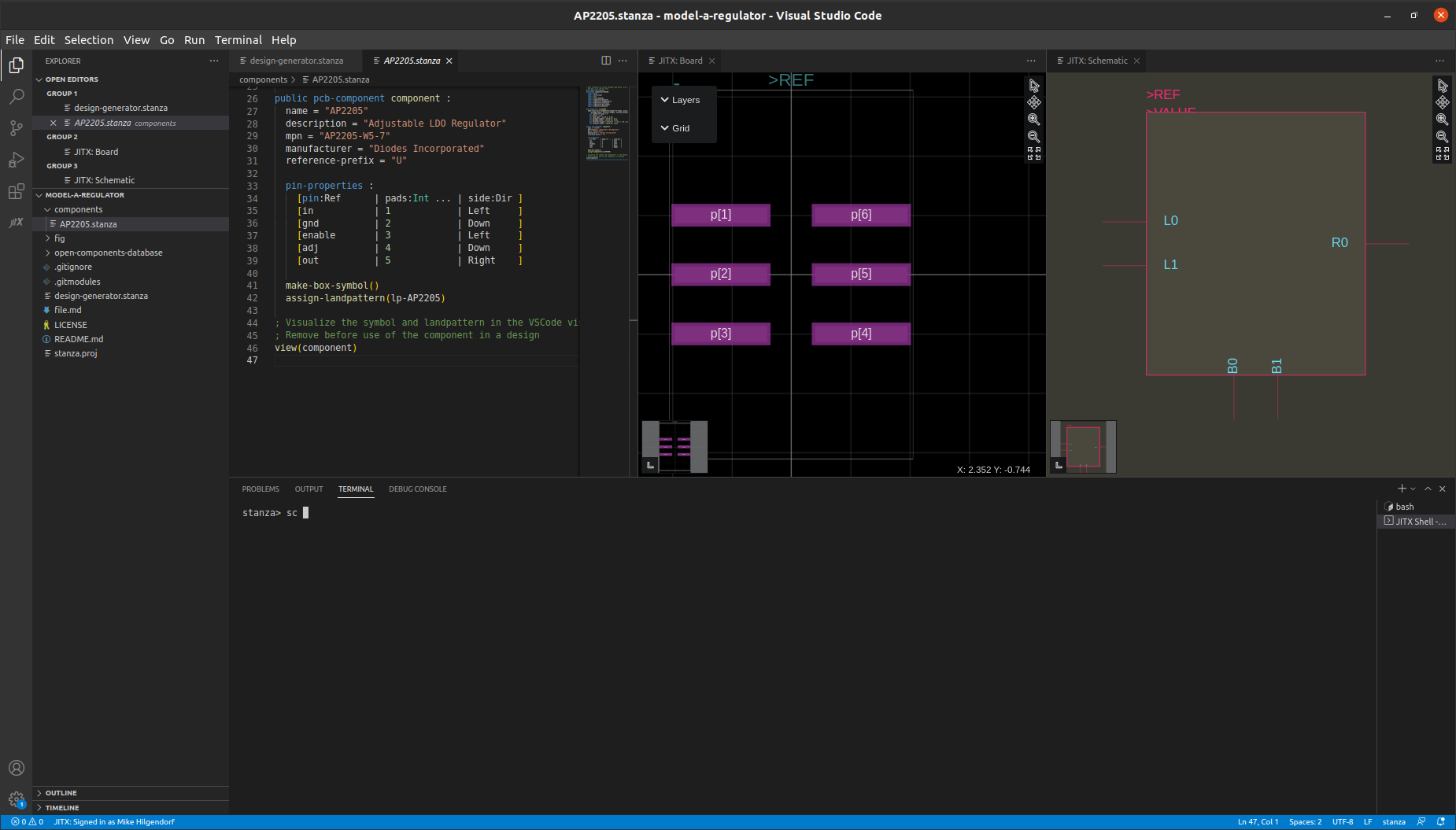

1. Searching for components

Open the JITX sidebar and click on Find Components. Search for:

TPS62080DSGR

Then click on the "Create Component" button. This adds a local code model of a component to your project.

To add it to your design, in main.stanza, change the my-design module to be:

pcb-module my-design:

inst buck : components/Texas-Instruments/TPS62080DSGR/component

You have added this component to your design, run it to see it appear in the schematic and layout.

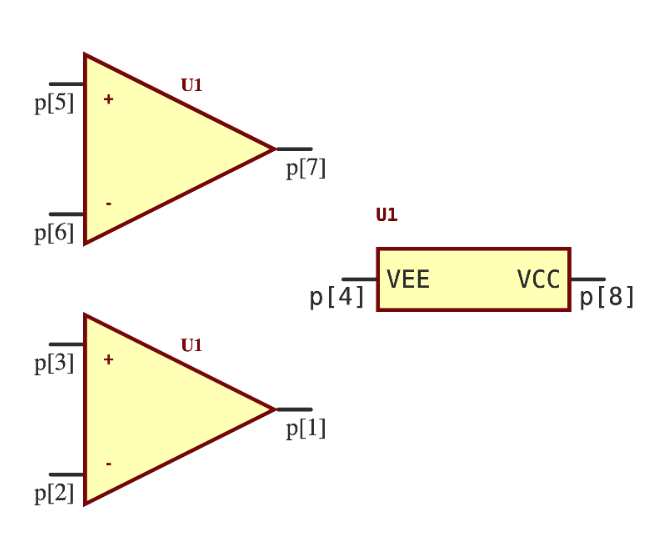

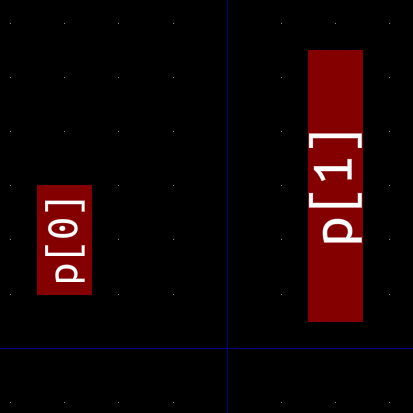

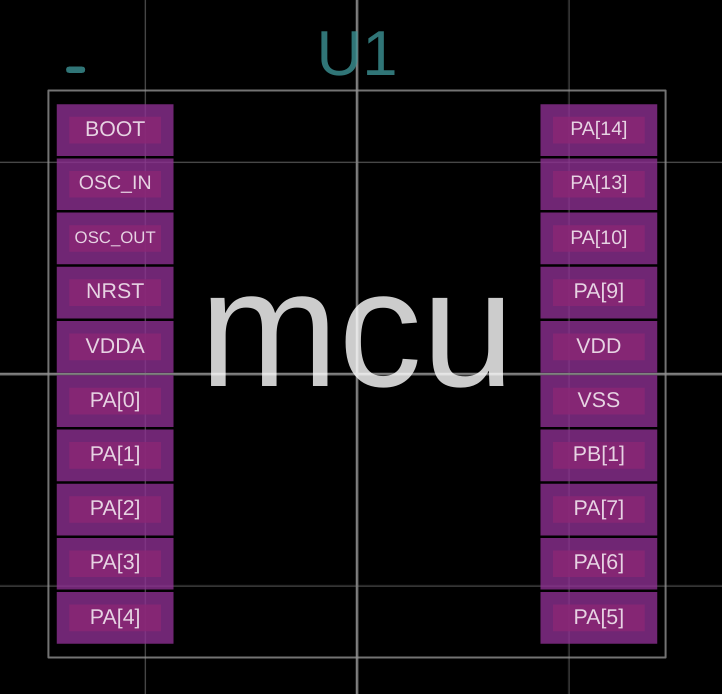

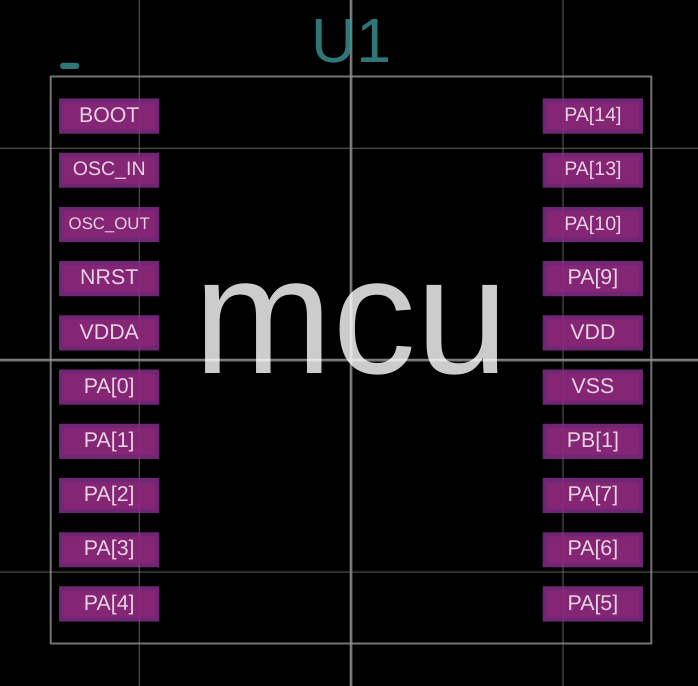

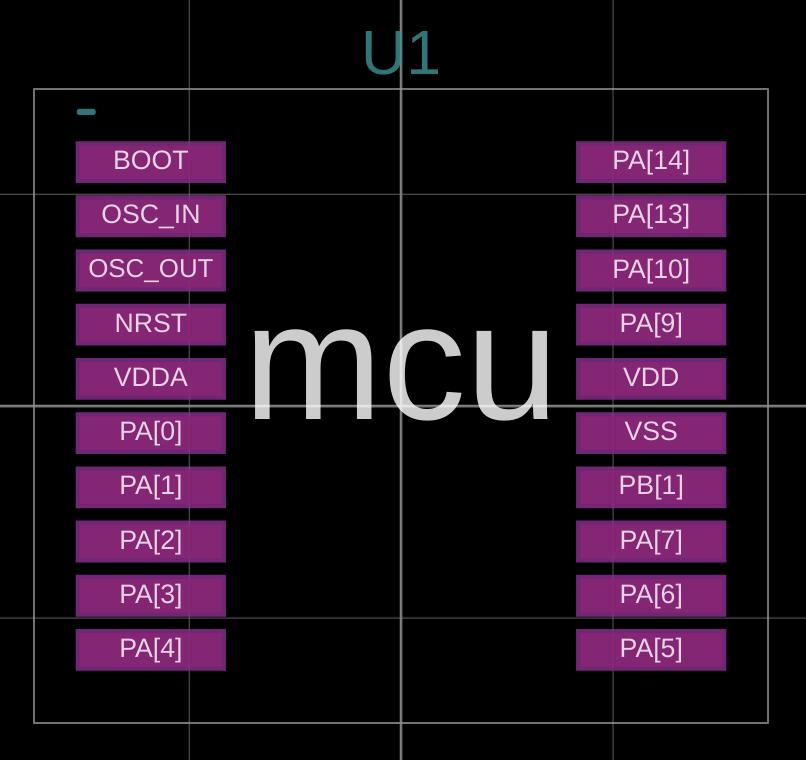

2. JITX component models

Open the components/Texas-Instruments/TPS62080DSGR.stanza file.

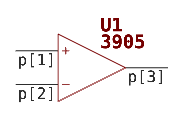

Delete the original pcb-symbol definition. In the pcb-component definition, shuffle the order of the pins, and replace the assign-symbol() line so that the new component body becomes:

pin-properties :

[pin:Ref | pads:Ref ... | side:Dir | electrical-type:String | bank:Int]

[VIN | p[8] | Left | "power_in" | 0]

[EN | p[1] | Left | "unspecified" | 0]

[MODE | p[3] | Left | "unspecified" | 0]

[GND | p[2] p[9] | Left | "power_in" | 0]

[PG | p[6] | Right | "unspecified" | 0]

[SW | p[7] | Right | "power_in" | 0]

[VOS | p[5] | Right | "unspecified" | 0]

[FB | p[4] | Right | "unspecified" | 0]

assign-landpattern(lp)

make-box-symbol()

3. Reusable circuits

Below the component definition in TPS62080DSGR.stanza, add:

public pcb-module module :

inst reg : components/Texas-Instruments/TPS62080DSGR/component

4. Using models from the database

Open the JITX sidebar and click on Find Components. Search for:

NR3015T1R0N

Then click on the "Copy Component" button, and paste it into the module:

public pcb-module module (-- output-voltage:Double = 3.3) :

inst buck : components/Texas-Instruments/TPS62080DSGR/component

inst L : database-part(["mpn" => "NR3015T1R0N", "manufacturer" => "Taiyo Yuden"])

To use the database-part function, you'll have to import generic-components at the top:

defpackage components/Texas-Instruments/TPS62080DSGR :

import core

import jitx

import jitx/commands

import ocdb/utils/box-symbol

import ocdb/utils/generic-components

Change main.stanza to use the new module:

pcb-module my-design:

inst buck : components/Texas-Instruments/TPS62080DSGR/module

5. Making connections with net

In the module definition in TPS62080DSGR.stanza, add ports and nets to build the circuit and expose an interface:

public pcb-module module (-- output-voltage:Double = 3.3) :

pin vin

pin vout

pin en

pin gnd

inst buck : components/Texas-Instruments/TPS62080DSGR/component

inst L : database-part(["mpn" => "NR3015T1R0N", "manufacturer" => "Taiyo Yuden"])

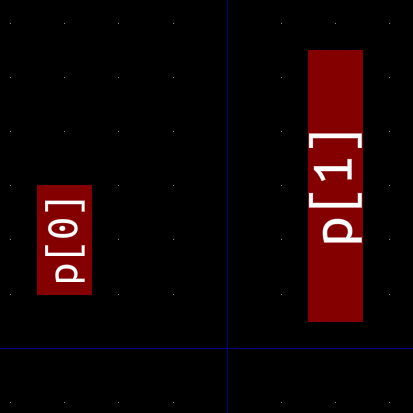

net (buck.SW L.p[1])

net (buck.VOS L.p[2] vout)

net (buck.VIN vin)

net (buck.EN en)

net (buck.GND gnd buck.MODE)

In main.stanza you can now net the module pins:

pcb-module my-design:

inst buck : components/Texas-Instruments/TPS62080DSGR/module

net (buck.vin buck.en)

6. Parametric components

In the module definition in TPS62080DSGR.stanza, add the input and output capacitors:

bypass-cap-strap(buck.VIN, buck.GND, 10.0e-6)

bypass-cap-strap(L.p[2], buck.GND, 22.0e-6)

7. Reusing a smart sub-circuit

In the module definition in TPS62080DSGR.stanza, add the voltage divider and attach it:

inst feedback : ocdb/modules/passive-circuits/voltage-divider(

source-voltage = typ(3.3),

divider-output = 0.45 +/- (3 %),

current = 100.0 * 100.0e-9)

net (feedback.in L.p[2])

net (feedback.out buck.FB)

net (feedback.lo buck.GND)

8. Making the parametric power regulator

Finally, change the module definition in TPS62080DSGR.stanza to accept an output-voltage argument, and pass that in to the voltage divider. Here is the completed module:

public pcb-module module (-- output-voltage:Double = 3.3) :

pin vin

pin vout

pin en

pin gnd

inst buck : components/Texas-Instruments/TPS62080DSGR/component

inst L : database-part(["mpn" => "NR3015T1R0N", "manufacturer" => "Taiyo Yuden"])

net (buck.SW L.p[1])

net (buck.VOS L.p[2] vout)

net (buck.VIN vin)

net (buck.EN en)

net (buck.GND gnd buck.MODE)

bypass-cap-strap(buck.VIN, buck.GND, 10.0e-6)

bypass-cap-strap(L.p[2], buck.GND, 22.0e-6)

inst feedback : ocdb/modules/passive-circuits/voltage-divider(

source-voltage = typ(output-voltage),

divider-output = 0.45 +/- (3 %),

current = 100.0 * 100.0e-9)

net (feedback.in L.p[2])

net (feedback.out buck.FB)

net (feedback.lo buck.GND)

Change main.stanza you can now net the module pins:

pcb-module my-design:

inst buck : components/Texas-Instruments/TPS62080DSGR/module(output-voltage = 3.3)

net (buck.vin buck.en)

Next: Tutorial: Schematic and layout

Completed code for Tutorial: Create a circuit

; This file is generated based on the parts database query below:")

; database-part(["manufacturer" => "Texas Instruments", "mpn" => "TPS62080DSGR"])

#use-added-syntax(jitx)

defpackage components/Texas-Instruments/TPS62080DSGR :

import core

import jitx

import jitx/commands

import ocdb/utils/box-symbol

import ocdb/utils/generic-components

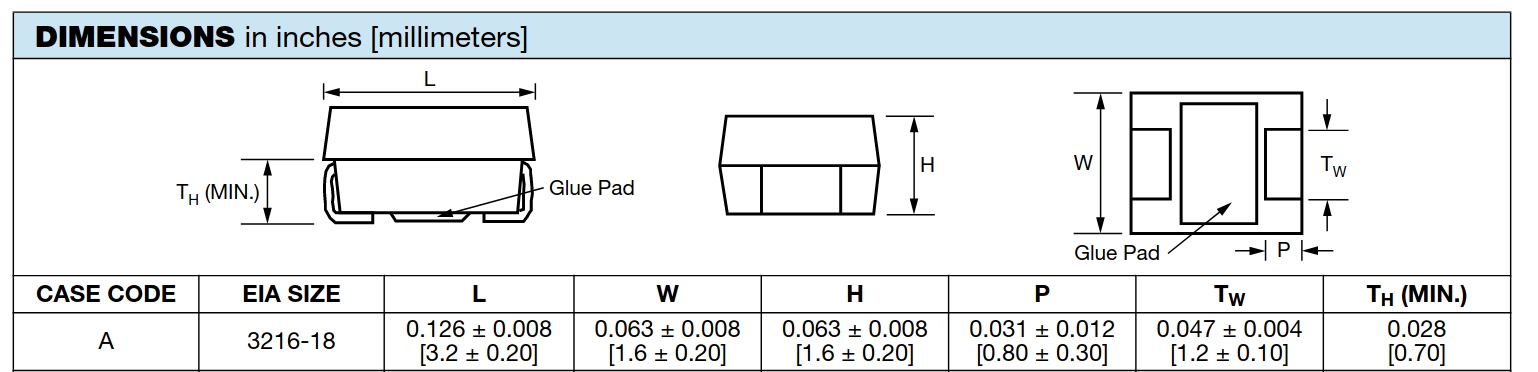

pcb-pad rectangle-smd-pad :

name = "rectangle-smd-pad"

type = SMD

shape = Rectangle(0.280, 0.505)

layer(SolderMask(Top)) = Rectangle(0.382, 0.607)

layer(Paste(Top)) = Rectangle(0.382, 0.607)

pcb-pad rectangle-smd-pad-1 :

name = "rectangle-smd-pad-1"

type = SMD

shape = Rectangle(1.600, 0.900)

layer(SolderMask(Top)) = Rectangle(1.702, 1.002)

layer(Paste(Top)) = Rectangle(1.702, 1.002)

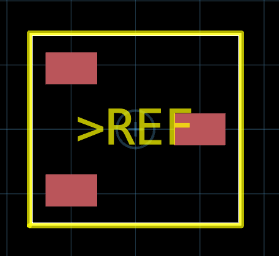

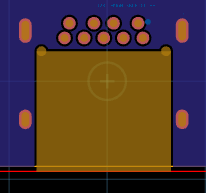

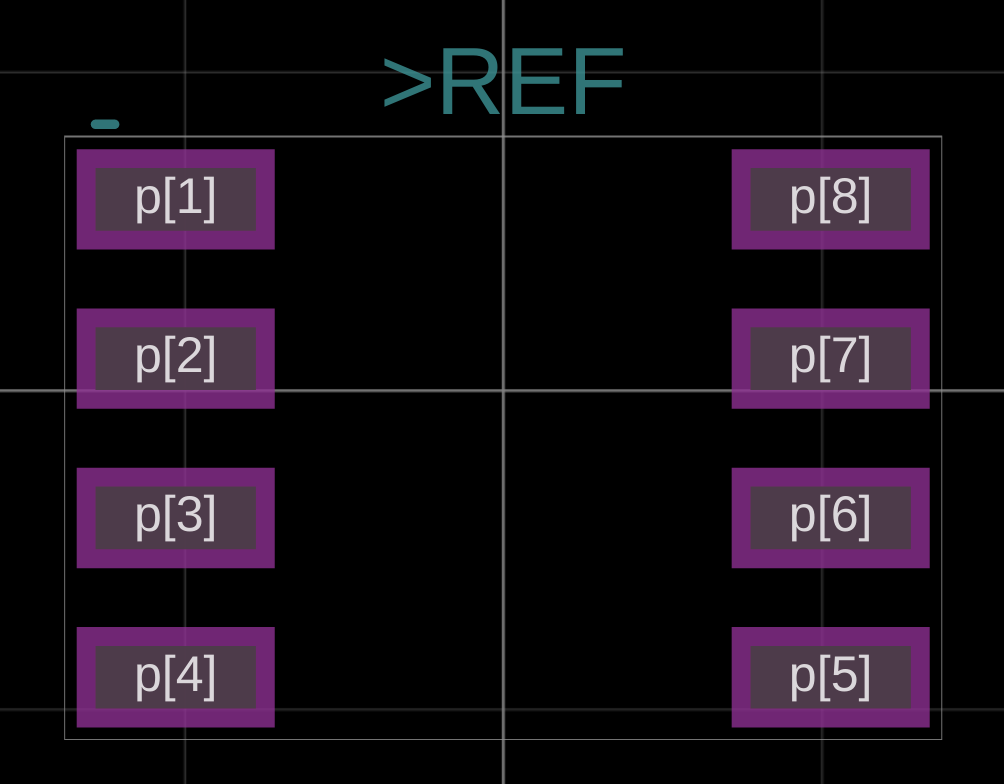

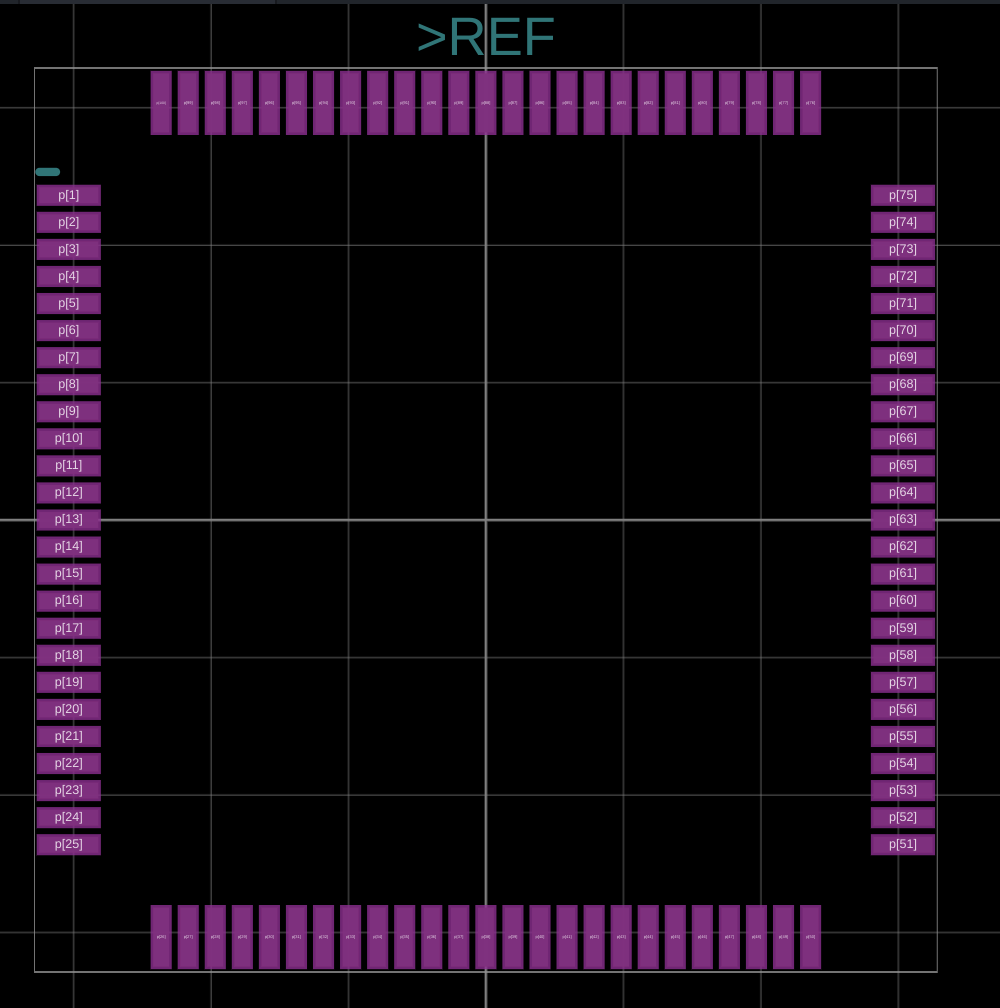

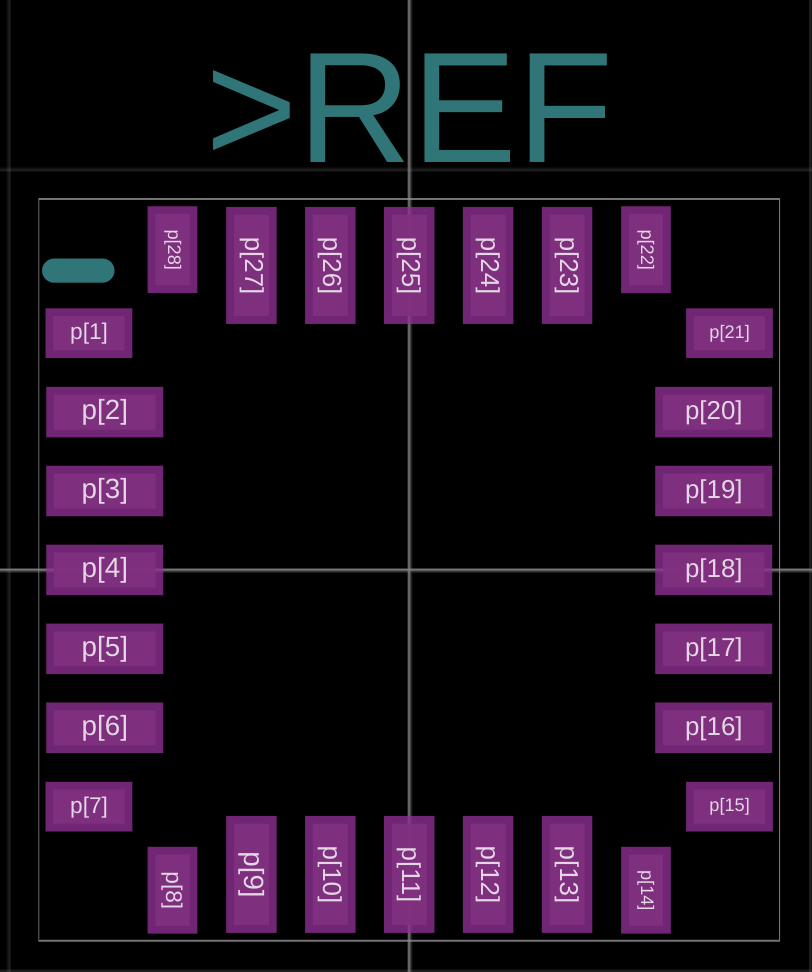

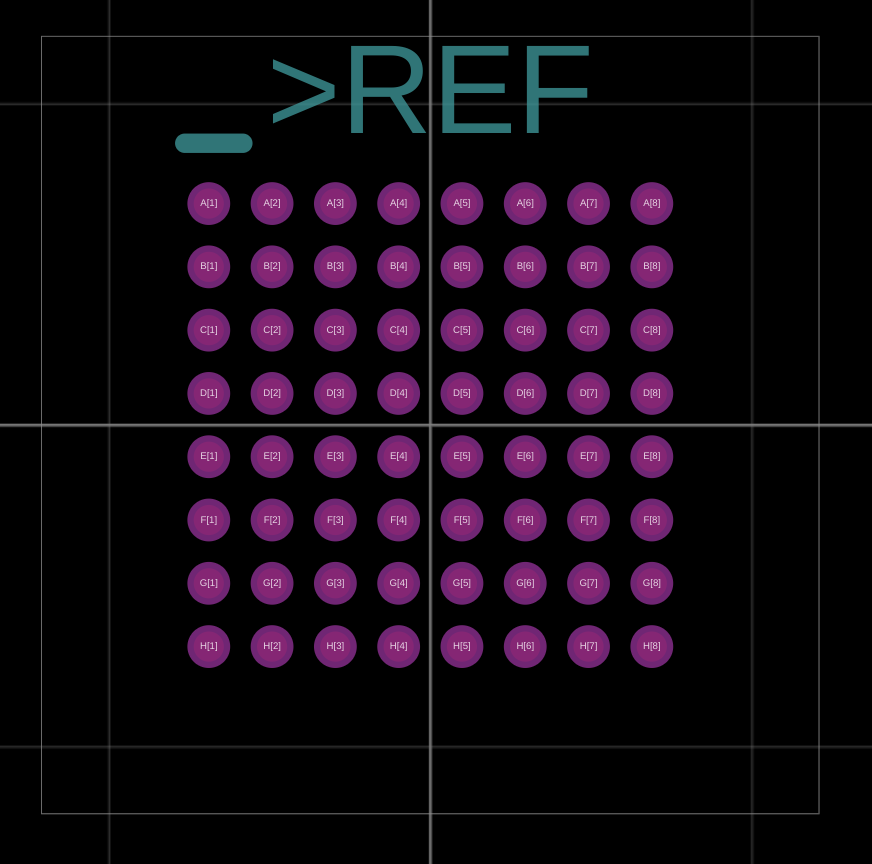

pcb-landpattern lp :

pad p[1] : rectangle-smd-pad at loc(-0.750, -0.928) on Top

pad p[2] : rectangle-smd-pad at loc(-0.250, -0.928) on Top

pad p[3] : rectangle-smd-pad at loc(0.250, -0.928) on Top

pad p[4] : rectangle-smd-pad at loc(0.750, -0.928) on Top

pad p[5] : rectangle-smd-pad at loc(0.750, 0.928) on Top

pad p[6] : rectangle-smd-pad at loc(0.250, 0.928) on Top

pad p[7] : rectangle-smd-pad at loc(-0.250, 0.928) on Top

pad p[8] : rectangle-smd-pad at loc(-0.750, 0.928) on Top

pad p[9] : rectangle-smd-pad-1 at loc(0.0, -0.000499999999988177) on Top

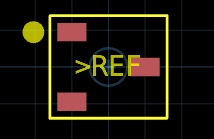

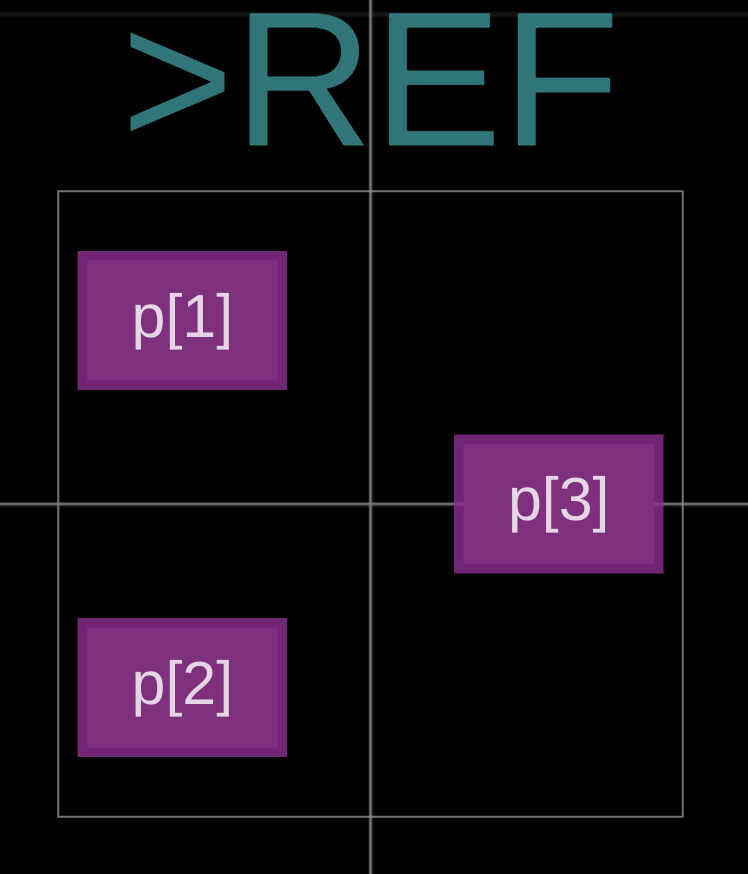

layer(Silkscreen("F-SilkS", Top)) = Text(">REF", 0.5, W, loc(-0.750, 2.937), "", TrueTypeFont, false, false)

layer(CustomLayer("Fab", Top)) = Text(">VALUE", 0.5, W, loc(-0.750, 1.937), "", TrueTypeFont, false, false)

layer(Silkscreen("F-SilkS", Top)) = Line(0.152, [Point(1.076, 1.077), Point(1.076, -1.077)])

layer(Silkscreen("F-SilkS", Top)) = Line(0.152, [Point(-1.076, -1.077), Point(-1.076, 1.077)])

layer(CustomLayer("Fab", Top)) = Polyline(0.060, [

Arc(-1.000, -1.000, 0.030, 0.0, -360.000)])

layer(CustomLayer("Fab", Top)) = Polyline(0.300, [

Arc(-0.762, -1.271, 0.150, 0.0, -360.000)])

layer(Silkscreen("F-SilkS", Top)) = Polyline(0.200, [

Arc(-0.750, -1.481, 0.100, 0.0, -360.000)])

layer(Courtyard(Top)) = Rectangle(2.304, 2.462)

model3d = Model3D("../../3d-models/jitx-64d12e58b789d8dc4b77c71a.stp",

Vec3D(0.0, 0.0, 0.0),

Vec3D(1.000, 1.000, 1.000),

Vec3D(0.0, 0.0, 0.0),

[],

)

public pcb-component component :

name = "C130071"

description = "Step-down type Adjustable 0.5V~4V 1.2A 2.3V~6V DFN-8-EP(2x2) DC-DC Converters ROHS"

manufacturer = "Texas Instruments"

mpn = "TPS62080DSGR"

datasheet = "https://datasheet.lcsc.com/lcsc/1806051415_Texas-Instruments-TPS62080DSGR_C130071.pdf"

reference-prefix = "U"

pin-properties :

[pin:Ref | pads:Ref ... | side:Dir | electrical-type:String | bank:Int]

[VIN | p[8] | Left | "power_in" | 0]

[EN | p[1] | Left | "unspecified" | 0]

[MODE | p[3] | Left | "unspecified" | 0]

[GND | p[2] p[9] | Left | "power_in" | 0]

[PG | p[6] | Right | "unspecified" | 0]

[SW | p[7] | Right | "power_in" | 0]

[VOS | p[5] | Right | "unspecified" | 0]

[FB | p[4] | Right | "unspecified" | 0]

assign-landpattern(lp)

make-box-symbol()

property(self.category) = "ic"

property(self.manufacturer_aliases) = ["Texas Instruments"]

property(self.mpn_aliases) = ["TPS62080DSGR"]

property(self.cofactr_id) = "IC8WHGVOE6M1"

property(self.reference_prefix) = "U"

property(self.trust) = "low"

property(self.x) = 2.304

property(self.y) = 2.462

property(self.area) = 5.672

property(self.case) = "DFN-8(2x2)"

property(self.mounting) = "smd"

public pcb-module module (-- output-voltage:Double = 3.3) :

pin vin

pin vout

pin en

pin gnd

inst buck : components/Texas-Instruments/TPS62080DSGR/component

inst L : database-part(["mpn" => "NR3015T1R0N", "manufacturer" => "Taiyo Yuden"])

net (buck.SW L.p[1])

net (buck.VOS L.p[2] vout)

net (buck.VIN vin)

net (buck.EN en)

net (buck.GND gnd buck.MODE)

bypass-cap-strap(buck.VIN, buck.GND, 10.0e-6)

bypass-cap-strap(L.p[2], buck.GND, 22.0e-6)

inst feedback : ocdb/modules/passive-circuits/voltage-divider(

source-voltage = typ(output-voltage),

divider-output = 0.45 +/- (3 %),

current = 100.0 * 100.0e-9)

net (feedback.in L.p[2])

net (feedback.out buck.FB)

net (feedback.lo buck.GND)

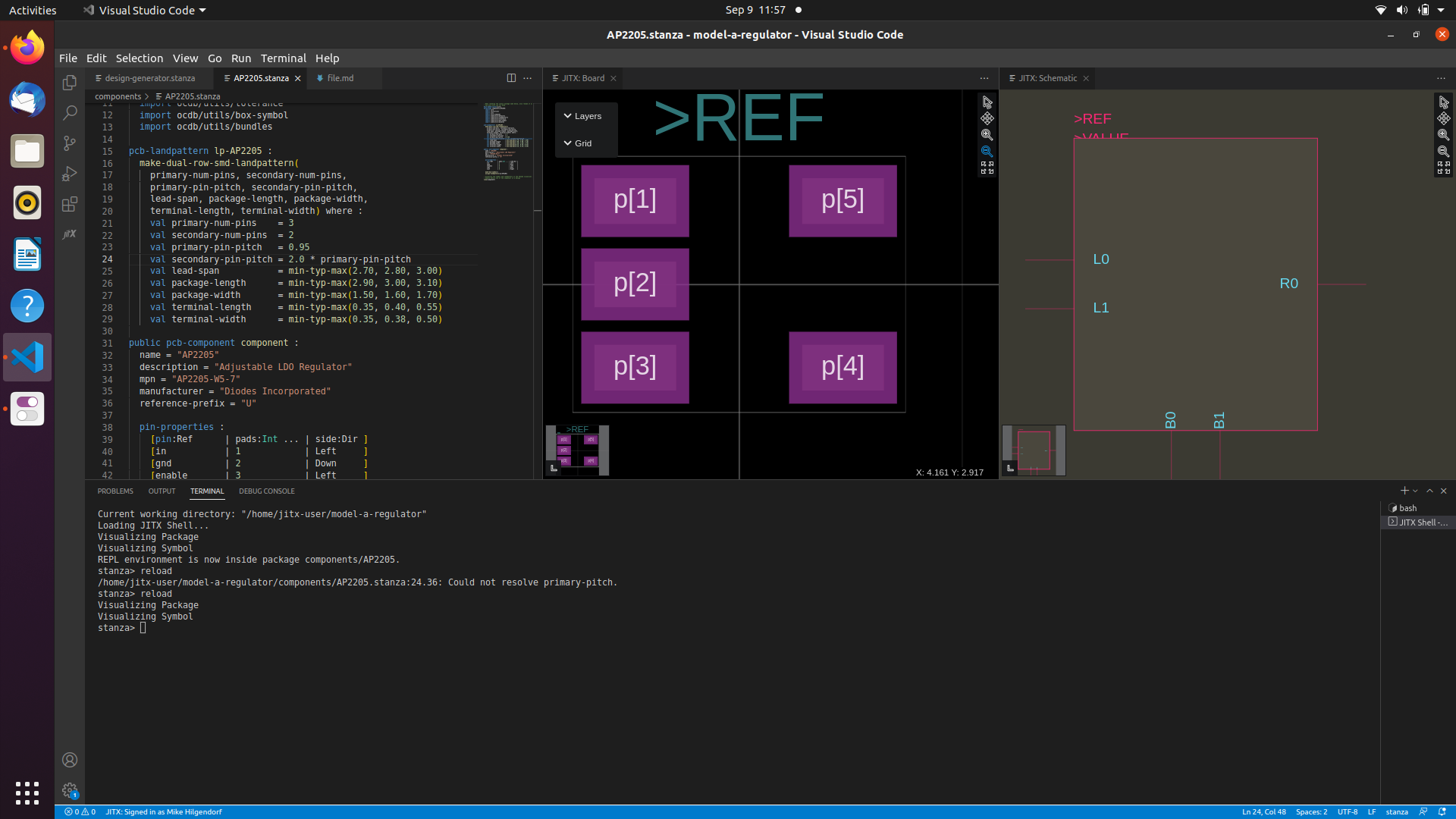

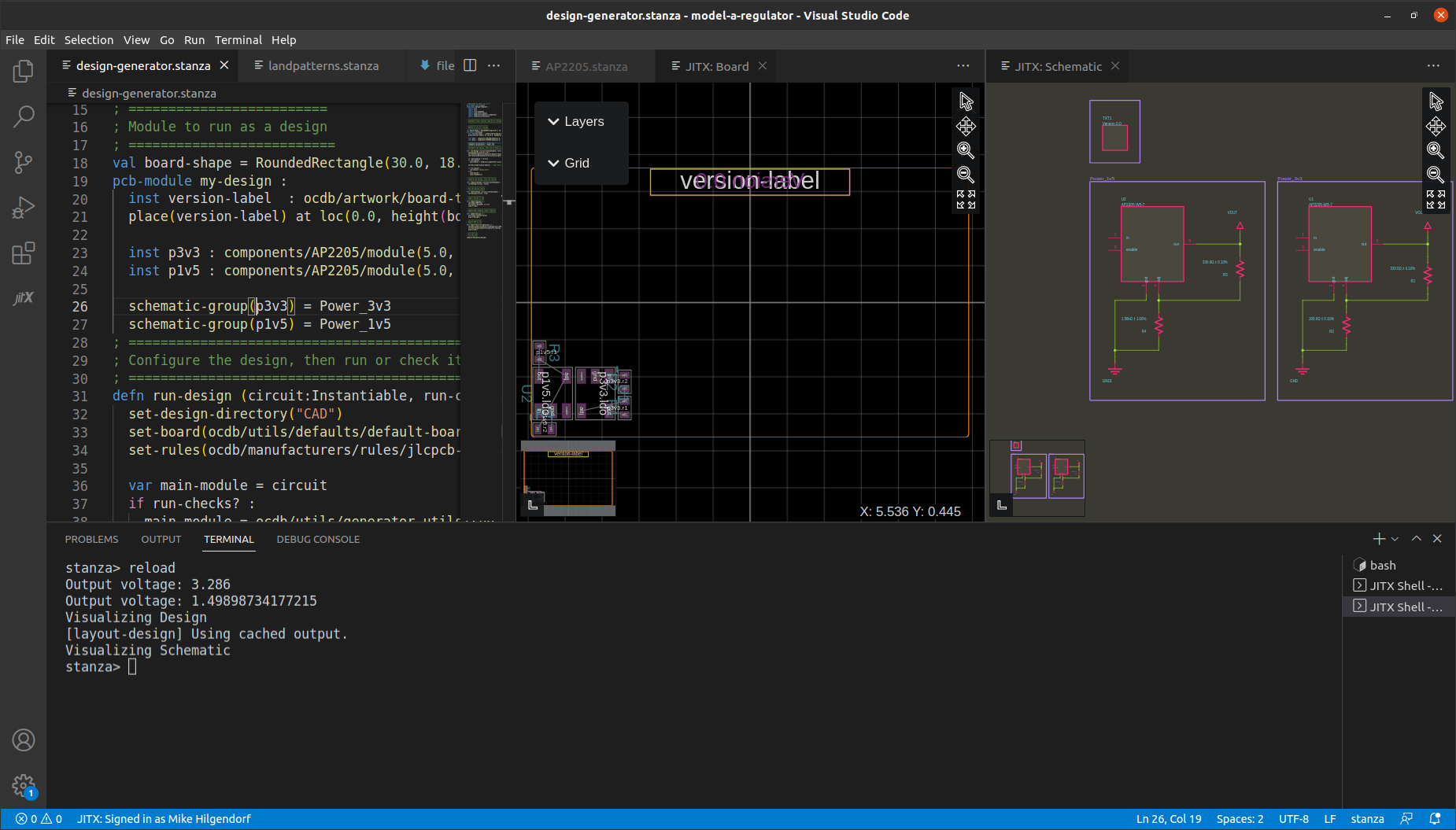

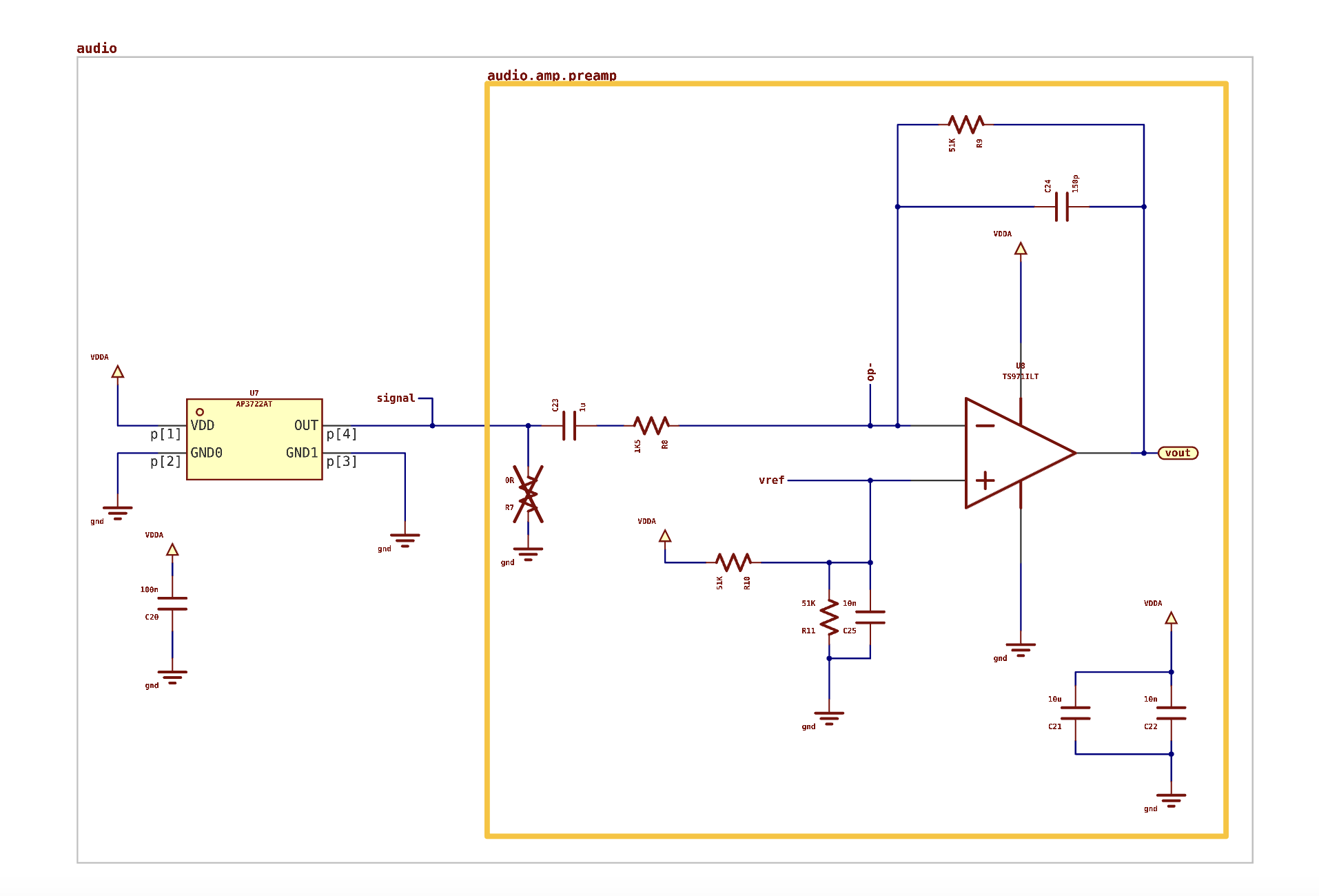

Tutorial: Schematic and layout

NOTE: Before starting this tutorial, you should have built the design from Tutorial: Create a circuit

You can follow along with this tutorial in the video above. Below is a transcript to make the code and text easier to read.

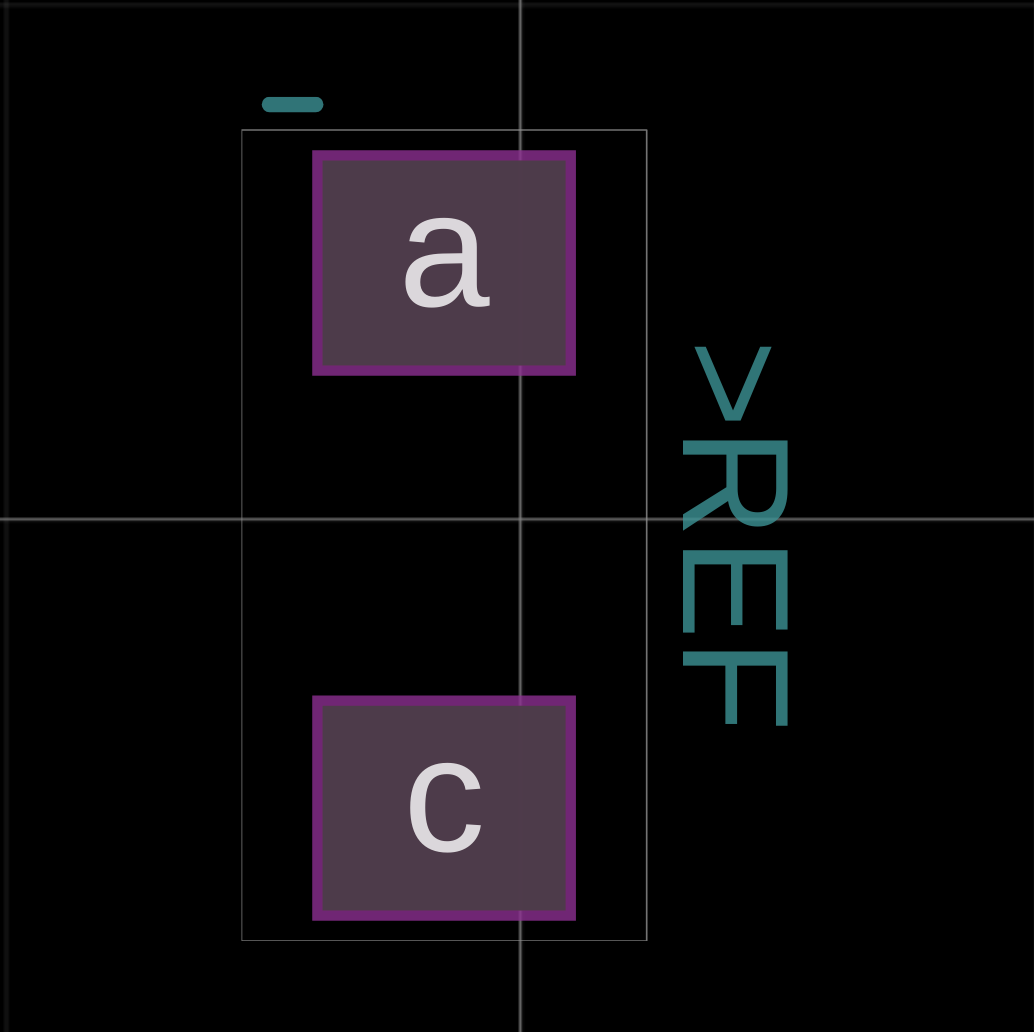

Naming nets and adding power symbols

In main.stanza, name the net attached to vin of the buck regulator module VIN:

pcb-module my-design :

inst buck : components/Texas-Instruments/TPS62080DSGR/module(output-voltage = 3.3)

net VIN (buck.vin buck.en)

Run the design to see the VIN label appear on the schematic.

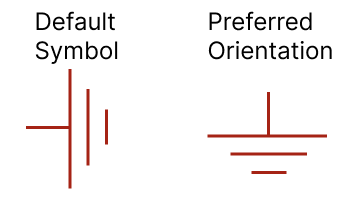

Next, create a net GND for ground, and assign a net symbol to it:

pcb-module my-design :

inst buck : components/Texas-Instruments/TPS62080DSGR/module(output-voltage = 3.3)

net VIN (buck.vin buck.en)

net GND (buck.gnd)

symbol(GND) = ocdb/utils/symbols/ground-sym

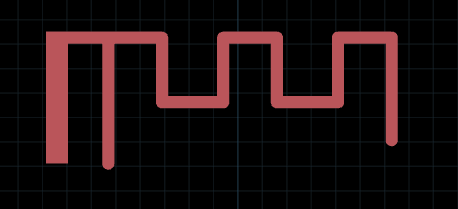

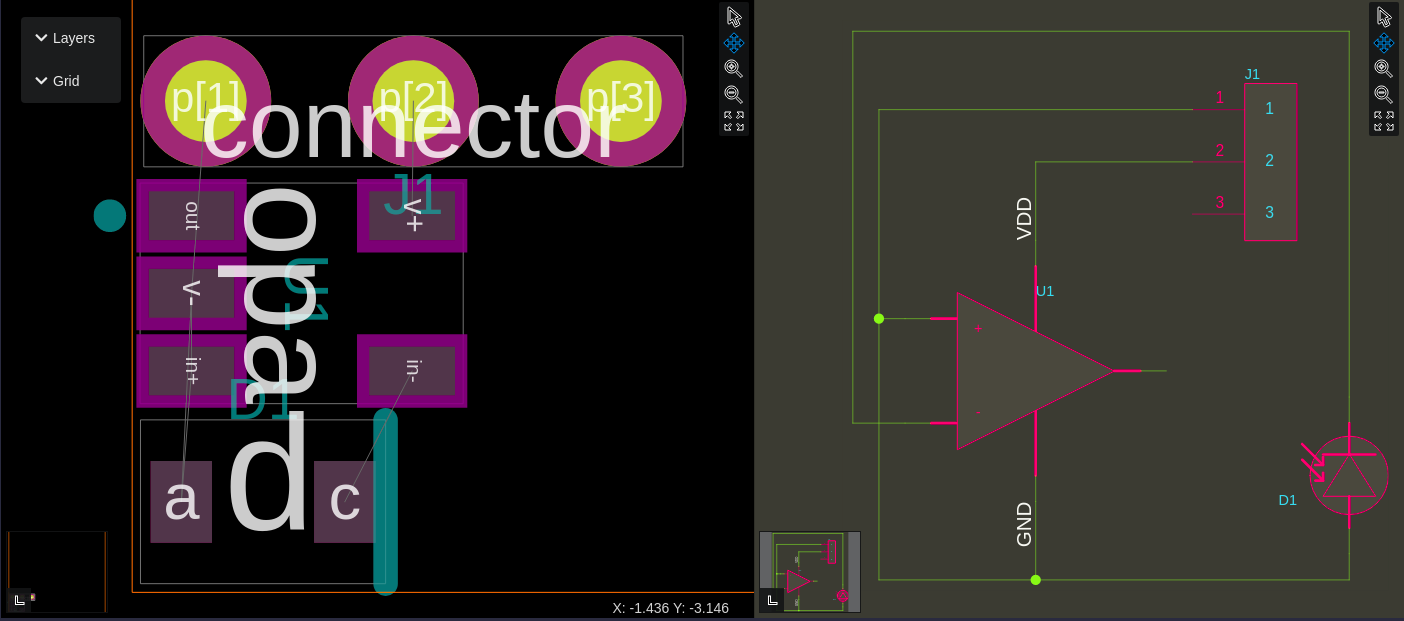

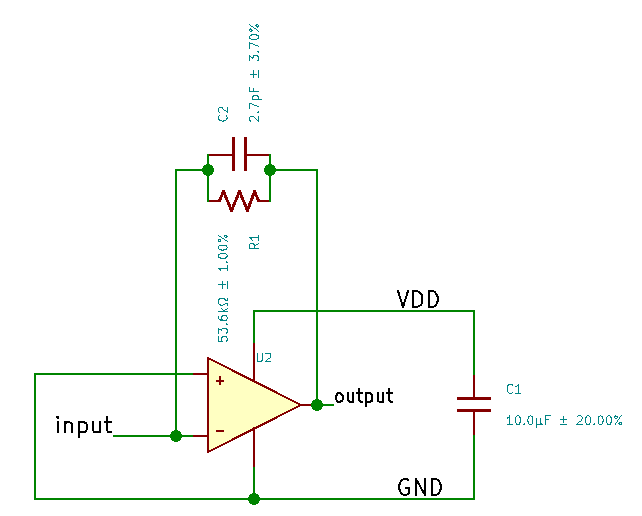

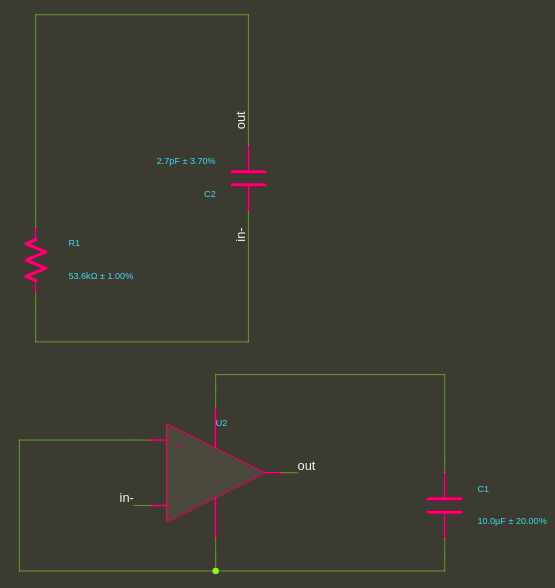

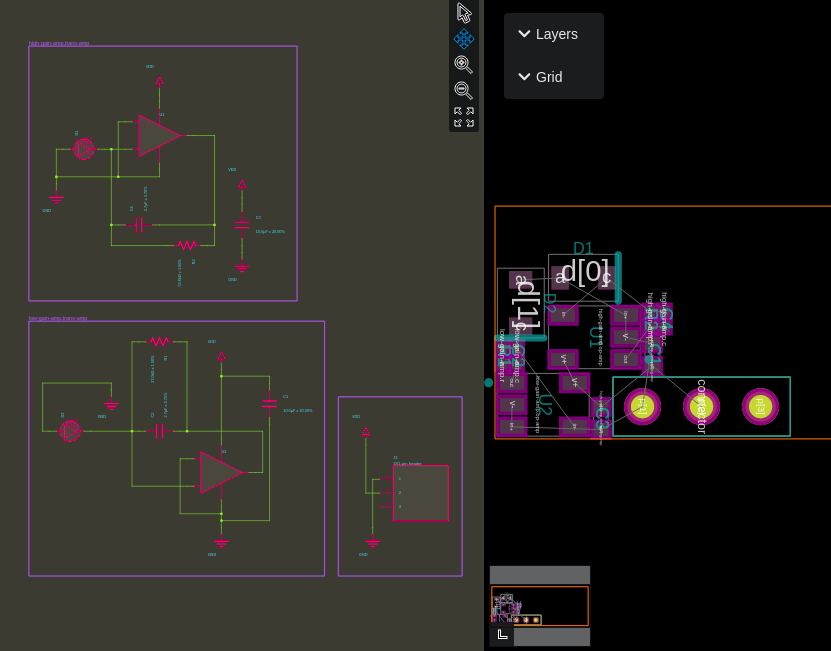

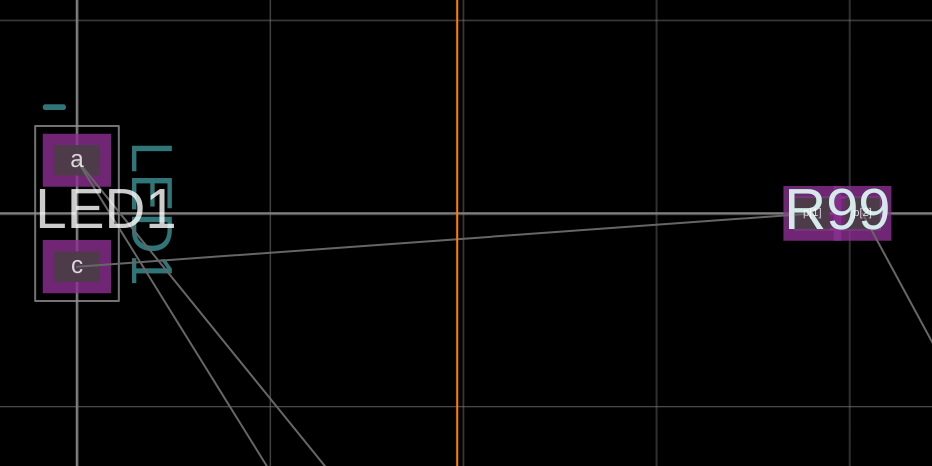

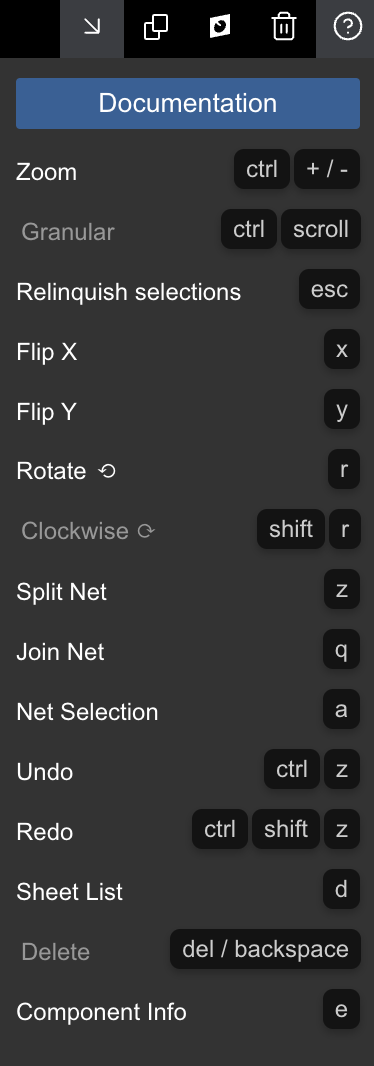

Schematic

The schematic UI is for changing the style of the schematic. Groups are automatically added based on the structure of the pcb-modules in your design.

All commands can be discovered from the (?) button in the upper-right of the screen.

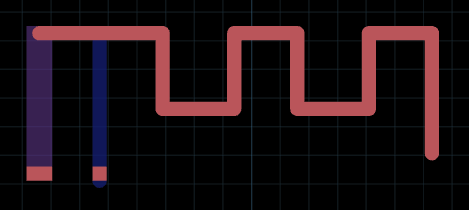

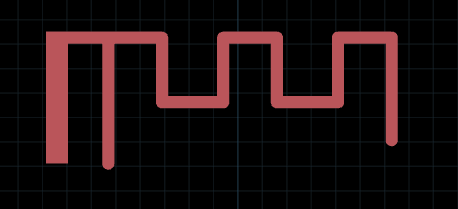

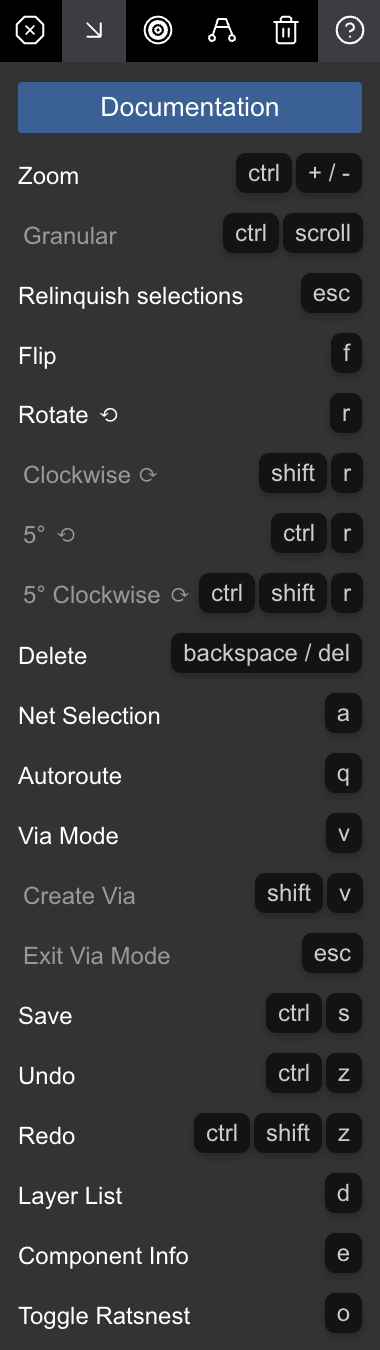

Layout

The layout UI is for completing the physical layout of your circuit board. You select which signals will be routed on which layer, and then route them with the autorouter. You can move components around, and the traces will follow.

You can use Adaptive for low inductance and low resistance routes, and generate pours automatically from dynamic traces.

You decide which pads need vias, and there is an auto-via tool to place and route those vias automatically. Vias are associated with those pads, and when you fan out a component those vias will travel with the component.

All commands can be discovered from the (?) button in the upper-right of the screen.

Completed Code for the Tutorial: Schematic and Layout Tutorial

; This file is generated based on the parts database query below:")

; database-part(["manufacturer" => "Texas Instruments", "mpn" => "TPS62080DSGR"])

#use-added-syntax(jitx)

defpackage components/Texas-Instruments/TPS62080DSGR :

import core

import jitx

import jitx/commands

import ocdb/utils/box-symbol

import ocdb/utils/generic-components

pcb-pad rectangle-smd-pad :

name = "rectangle-smd-pad"

type = SMD

shape = Rectangle(0.280, 0.505)

layer(SolderMask(Top)) = Rectangle(0.382, 0.607)

layer(Paste(Top)) = Rectangle(0.382, 0.607)

pcb-pad rectangle-smd-pad-1 :

name = "rectangle-smd-pad-1"

type = SMD

shape = Rectangle(1.600, 0.900)

layer(SolderMask(Top)) = Rectangle(1.702, 1.002)

layer(Paste(Top)) = Rectangle(1.702, 1.002)

pcb-landpattern lp :

pad p[1] : rectangle-smd-pad at loc(-0.750, -0.928) on Top

pad p[2] : rectangle-smd-pad at loc(-0.250, -0.928) on Top

pad p[3] : rectangle-smd-pad at loc(0.250, -0.928) on Top

pad p[4] : rectangle-smd-pad at loc(0.750, -0.928) on Top

pad p[5] : rectangle-smd-pad at loc(0.750, 0.928) on Top

pad p[6] : rectangle-smd-pad at loc(0.250, 0.928) on Top

pad p[7] : rectangle-smd-pad at loc(-0.250, 0.928) on Top

pad p[8] : rectangle-smd-pad at loc(-0.750, 0.928) on Top

pad p[9] : rectangle-smd-pad-1 at loc(0.0, -0.000499999999988177) on Top

layer(Silkscreen("F-SilkS", Top)) = Text(">REF", 0.5, W, loc(-0.750, 2.937), "", TrueTypeFont, false, false)

layer(CustomLayer("Fab", Top)) = Text(">VALUE", 0.5, W, loc(-0.750, 1.937), "", TrueTypeFont, false, false)

layer(Silkscreen("F-SilkS", Top)) = Line(0.152, [Point(1.076, 1.077), Point(1.076, -1.077)])

layer(Silkscreen("F-SilkS", Top)) = Line(0.152, [Point(-1.076, -1.077), Point(-1.076, 1.077)])

layer(CustomLayer("Fab", Top)) = Polyline(0.060, [

Arc(-1.000, -1.000, 0.030, 0.0, -360.000)])

layer(CustomLayer("Fab", Top)) = Polyline(0.300, [

Arc(-0.762, -1.271, 0.150, 0.0, -360.000)])

layer(Silkscreen("F-SilkS", Top)) = Polyline(0.200, [

Arc(-0.750, -1.481, 0.100, 0.0, -360.000)])

layer(Courtyard(Top)) = Rectangle(2.304, 2.462)

model3d = Model3D("../../3d-models/jitx-64d12e58b789d8dc4b77c71a.stp",

Vec3D(0.0, 0.0, 0.0),

Vec3D(1.000, 1.000, 1.000),

Vec3D(0.0, 0.0, 0.0),

[],

)

public pcb-component component :

name = "C130071"

description = "Step-down type Adjustable 0.5V~4V 1.2A 2.3V~6V DFN-8-EP(2x2) DC-DC Converters ROHS"

manufacturer = "Texas Instruments"

mpn = "TPS62080DSGR"

datasheet = "https://datasheet.lcsc.com/lcsc/1806051415_Texas-Instruments-TPS62080DSGR_C130071.pdf"

reference-prefix = "U"

pin-properties :

[pin:Ref | pads:Ref ... | side:Dir | electrical-type:String | bank:Int]

[VIN | p[8] | Left | "power_in" | 0]

[EN | p[1] | Left | "unspecified" | 0]

[MODE | p[3] | Left | "unspecified" | 0]

[GND | p[2] p[9] | Left | "power_in" | 0]

[PG | p[6] | Right | "unspecified" | 0]

[SW | p[7] | Right | "power_in" | 0]

[VOS | p[5] | Right | "unspecified" | 0]

[FB | p[4] | Right | "unspecified" | 0]

assign-landpattern(lp)

make-box-symbol()

property(self.category) = "ic"

property(self.manufacturer_aliases) = ["Texas Instruments"]

property(self.mpn_aliases) = ["TPS62080DSGR"]

property(self.cofactr_id) = "IC8WHGVOE6M1"

property(self.reference_prefix) = "U"

property(self.trust) = "low"

property(self.x) = 2.304

property(self.y) = 2.462

property(self.area) = 5.672

property(self.case) = "DFN-8(2x2)"

property(self.mounting) = "smd"

public pcb-module module (-- output-voltage:Double = 3.3) :

pin vin

pin vout

pin en

pin gnd

inst buck : components/Texas-Instruments/TPS62080DSGR/component

inst L : database-part(["mpn" => "NR3015T1R0N", "manufacturer" => "Taiyo Yuden"])

net (buck.SW L.p[1])

net (buck.VOS L.p[2] vout)

net (buck.VIN vin)

net (buck.EN en)

net (buck.GND gnd buck.MODE)

bypass-cap-strap(buck.VIN, buck.GND, 10.0e-6)

bypass-cap-strap(L.p[2], buck.GND, 22.0e-6)

inst feedback : ocdb/modules/passive-circuits/voltage-divider(

source-voltage = typ(output-voltage),

divider-output = 0.45 +/- (3 %),

current = 100.0 * 100.0e-9)

net (feedback.in L.p[2])

net (feedback.out buck.FB)

net (feedback.lo buck.GND)

JITX Reference

Reference materials refer to technical descriptions of JITX’s machinery and its operation. Things like descriptions of key classes, functions, and APIs would fall under this umbrella. This includes types, statements, and commands among other things.

- Types are classifications of circuit board concepts and define their possible values and operations.

- Statements are pieces of code, often one line each, that together define a design. Statements are what constructs ESIR (Electronic Systems Intermediate Representation) to create designs.

- Commands are function calls that retrieve information from or modify a design.

Examples

- Commands

pins (obj:JITXObject)retrieves all pins in the given JITXObject.set-rules (rules:Rules)assigns aRulesto your design.

- Statements

mpn = "TRS3122ERGER"assigns a component's mpn.port p : pin[2]creates a port with two pins.

- Types

- Top-level definitions have types including

LandPattern,SchematicSymbol, andBoard. They all subtypeJITXDef, meaning that objects with these types can perform the same operations as aJITXDef. - Local definitions have types including

LandPatternPadandSymbolPin. They all subtypeJITXObject.

- Top-level definitions have types including

JITX Statements

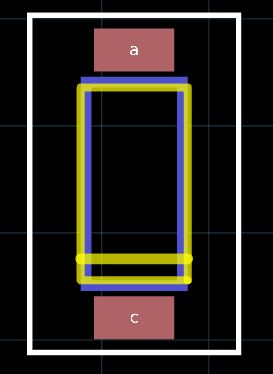

| Statement | Description |

|---|---|

pcb-board | Metadata of the board itself |

pcb-bundle | A collection of other top level statements |

pcb-check | A check on the correctness of our design |

pcb-component | A single device such as an IC or passive element. |

pcb-enum | A store for categorical variables |

pcb-landpattern | A component footprint/land pad. |

pcb-material | A material for a layer in the stackup |

pcb-module | A single reusable module which may contain other top level statements. |

pcb-pad | A single pad on the physical device/footprint |

pcb-rules | Fab house rules (tolerances, trace widths, |

pcb-routing-structure | Single-Ended Routing Structures |

pcb-differential-routing-structure | Differential Routing Structures |

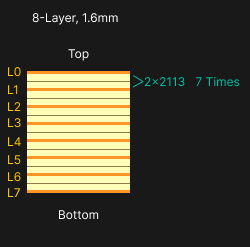

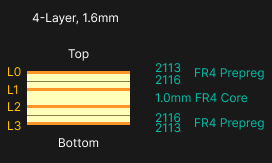

pcb-stackup | The stackup for the board |

pcb-via | The via definition and parameters |

pcb-struct | A way to group several related variables. |

pcb-symbol | A schematic symbol |

Boards

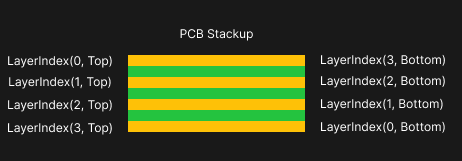

A pcb-board statement defines the physical structure of the circuit board for a design. A board contains a stackup, boundary, signal boundary, and optional layer statements.

Signature

pcb-board board-name (arg1:Type1, ...):

name = <String|False>

description = <String|False>

boundary = <Shape>

signal-boundary = <Shape|False>

stackup = <Stackup>

vias = [<Via>, <Via>, ... ]

layer(<LayerSpecifier>) = <Shape>

...

The expression name board-name uniquely identifies this board definition in the current context.

The argument list (arg1:Type1, ...) is optional and provides a means of constructing parameterized board definitions.

- Required Parameters

boundary- This is aShapethat defines the physical board outline.- This shape must be a simple polygon.

- This means that it must not have any holes or self-intersections.

stackup- User must provide a pcb-stackup definition.- This defines the copper and dielectric layer stackup.

vias- Tuple of pcb-via definitions.- These definitions limit what vias are allowed to be placed on the board.

- Only the vias present in this tuple will populate the drop-down via menu in the board tool.

- Optional Parameters

name- Optional string to provide a human readable name, mostly for the UI. If not present, then the expression name will be used.description- Optional string to describe this object. This is primarily for documentation and use in the UI.signal-boundary- This is an optionalShapethat defines what region of the board the router is allowed to route copper.- This shape must be a simple polygon.

- If not provided, the board definition will re-use the

boundaryshape for this parameter. - If provided, this shape must be no larger than the

boundaryshape. If this shape exceeds theboundaryshape, then the JITX runtime will raise an error.

layer()- Optional layer statements that allow the user to introduce geometry on any of the layers of the board.

Usage

The pcb-board definition is passed to the JITX runtime via the set-board function.

val board-shape = Rectangle(60.0, 40.0)

val my-stackup = ocdb/manufacturers/stackups/jlcpcb-jlc2313

pcb-via default-th:

start = Top

stop = Bottom

diameter = 0.65

hole-diameter = 0.4

type = MechanicalDrill

tented = true

pcb-board my-circuit-board :

stackup = my-stackup

boundary = board-shape

signal-boundary = offset(board-shape, -0.5)

vias = [default-th]

...

set-board(my-circuit-board)

The OCDB library has many predefined stackups that can be useful for building prototypes.

Notice the use of the offset function to construct a signal-boundary that is slightly inset from the board boundary.

Using Arguments

Parameterized board definitions can be useful when constructing common structures. Building on the previous example:

val STD-FIXTURE-SHAPE = RoundedRectangle(100.0, 40.0, 1.0)

pcb-board fixture-board (

base-stackup:Stackup,

--

outline:Shape = STD-FIXTURE-SHAPE,

sig-buffer:Double = 0.5

) :

name = to-string("fixture-%_-%_" % [outline, sig-buffer])

stackup = base-stackup

boundary = outline

signal-boundary = offset(outline, (- sig-buffer))

vias = [default-th]

...

val my-stackup = ocdb/manufacturers/stackups/jlcpcb-jlc2313

; Example #1

val brd = fixture-board(my-stackup)

; Example #2

val brd = fixture-board(my-stackup, sig-buffer = 1.0)

set-board( brd )

In this example, we demonstrate the use of optional keyword arguments for parametrically defining the board for our design.

Here the sig-buffer argument is a keyword argument with a default value of 0.5. This forces the signal-boundary to be 0.5mm smaller than the boundary shape on all sides

of the board.

Making it a keyword argument provides better readability of the code - we don't have to wonder whether that second argument was supposed to be the outline shape or the sig-buffer.

It is often convenient to include a name constructed from the parameters so that we can differentiate two different pcb-board definitions constructed with this function.

Using Generators

Generators are a tool to compose reusable features into a definition.

defn set-boundary (outline:Shape -- sig-buffer:Double = 0.5) :

inside pcb-board:

boundary = outline

signal-boundary = offset(outline, (- sig-buffer))

val board-shape = Rectangle(60.0, 40.0)

pcb-board circuit-board-2 :

stackup = my-stackup

vias = [default-th]

set-boundary(board-shape)

...

set-board(circuit-board-2)

The set-boundary function is a generator. Notice the use of the inside pcb-board syntax. When set-boundary is called from within the context of a pcb-board definition, it can create any of the expected pcb-board parameters. In this particular instance, the set-boundary function sets the boundary and signal-boundary parameters.

The resulting circuit-board-2 definition would be equivalent to:

val board-shape = Rectangle(60.0, 40.0)

pcb-board equivalent-circuit-board :

stackup = my-stackup

vias = [default-th]

boundary = board-shape

signal-boundary = offset(board-shape, -0.5)

Calling set-boundary from any other context (ie, a regular function or a pcb-module) will elicit an error because the boundary = syntax will be unknown.

Name

The name statement is the optional name field of a JITX object. Use it to store a descriptive name as a String. This name will often be used in the UI in place of the object's expression name for better readability.

Signature

name = <String>

This statement is optional. The default value will be the definition's symbol name in case no name statement is found in a definition.

Any string is a valid name value.

Usage

Literal String Names

pcb-component component :

name = "ADM7150"

pcb-module band-pass-filter :

name = "Band-pass filter"

The examples name = "ADM7150" and name = "Band-pass filter" use a String liternal for the name.

Formatted Strings

pcb-pad smd-pad (anchor:Anchor, w:Double, h:Double) :

name = to-string("%_x%_ %_ SMD Pad" % [w,h,anchor])

pcb-landpattern test-lp:

pad p[1] : smd-pad(C, 0.6, 0.7) at loc(x0,y0)

We can also construct strings using formatting routes and parameter arguments for a particular definition. In this example, the constructed smd-pad name property would be 0.6x0.7 C SMD Pad

Description

The description statement is the optional descriptive field of a JITX object. Use it to store a description of the object for human designers reading JITX, and to make the object easier to find via text search. This description also shows up in the UI, such as the design explorer, to provide more insight into particular components and modules in the design.

Signature

description = <String|False>

This statement is optional. The default value will be false in case no description statement is found in a definition.

Any string is a valid description value.

Each JITX definition may have exactly one description statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Examples

; We can use string literals to describe a particular component.

pcb-component analog-devices-ADM7150 :

description = "800 mA Ultralow Noise, High PSRR, RF Linear Regulator"

; We can use string formatting to construct descriptions based on variables

; or arguments to a JITX Definition

pcb-module band-pass-filter (high-cut:Double, low-cut:Double) :

description = to-string(

"Band-pass Filter - Highpass = %_ Hz and Lowpass = %_ Hz." % [high-cut, low-cut]

)

Layer

The layer statement is used to create geometry on the non-copper layers of a circuit board. The layer() statement is valid in the following contexts:

Signature

layer(<LayerSpecifier>) = <Shape>

<LayerSpecifier>- A LayerSpecifier instance that identifies which non-copper layer to apply the provided geometry to.<Shape>- AShapeinstance that defines the geometry that will be created on the specified layer.

Usage

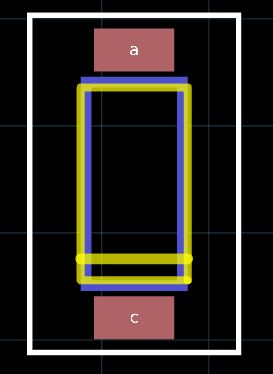

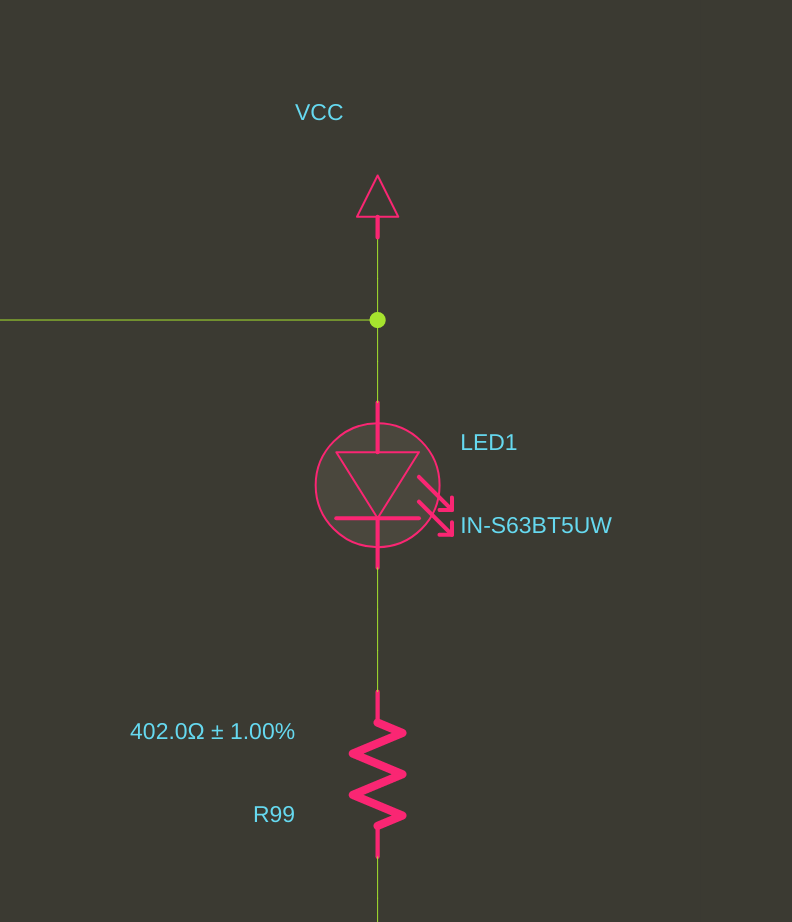

The most common usage of the layer() statement is in pcb-landpattern:

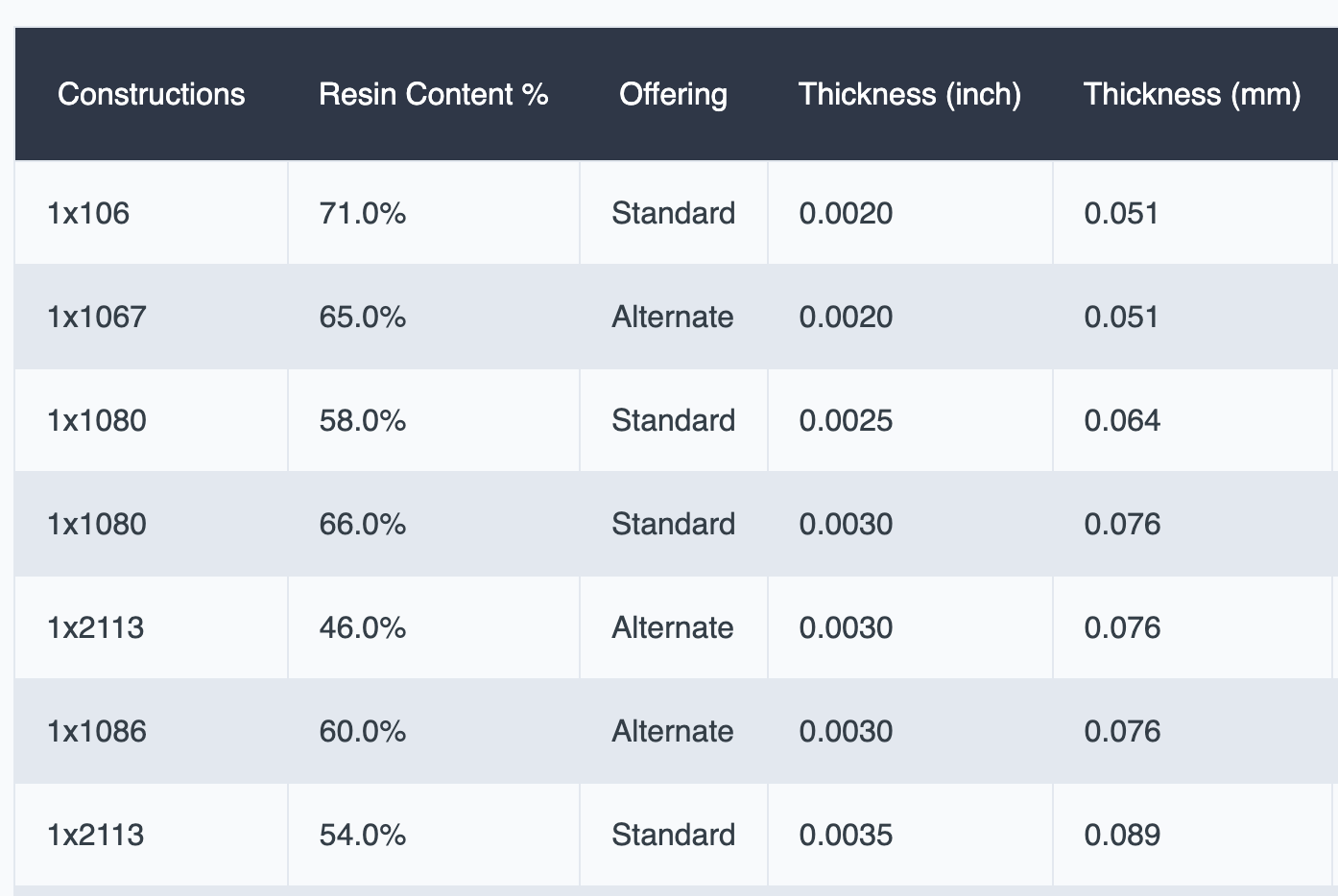

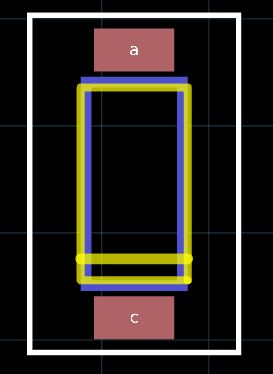

pcb-landpattern diode-lp :

pad c : smd-pad(0.4, 0.75) at loc(-1.25, 0.0) on Top

pad a : smd-pad(0.4, 0.75) at loc(1.25, 0.0) on Top

layer(Silkscreen("body", Top)) = LineRectangle(1.8, 1.0)

layer(Silkscreen("body", Top)) = Line(0.1, [Point(-0.70, -0.5), Point(-0.70, 0.5)])

layer(Courtyard(Top)) = Rectangle(3.2, 2.0)

layer(ForbidCopper(LayerIndex(0))) = Rectangle(2.0, 1.0)

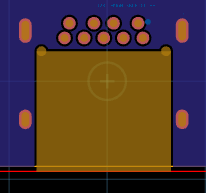

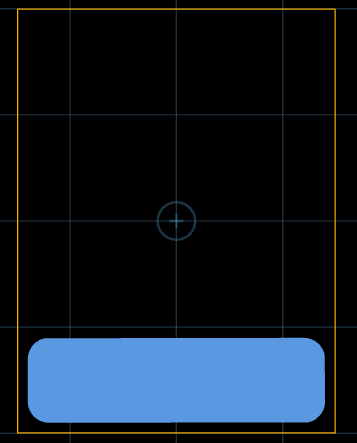

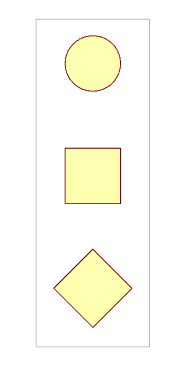

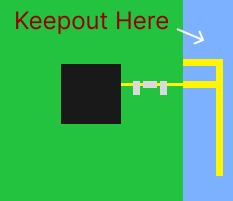

This will construct a landpattern that looks like this:

Notice the silkscreen in yellow with cathode marker. The blue box is the ForbidCopper layer on the Top Layer. Red is the top copper pads for the cathode c and anode a.

The white bounding rectangle is the Courtyard layer.

See LayerSpecifier for more information about specific layers.

Cutouts

When constructing cutouts in the board layout, your best bet is to use a solid region as opposed to a line. A line can confuse the routing engine into thinking that there are two physically separate regions where copper can be placed.

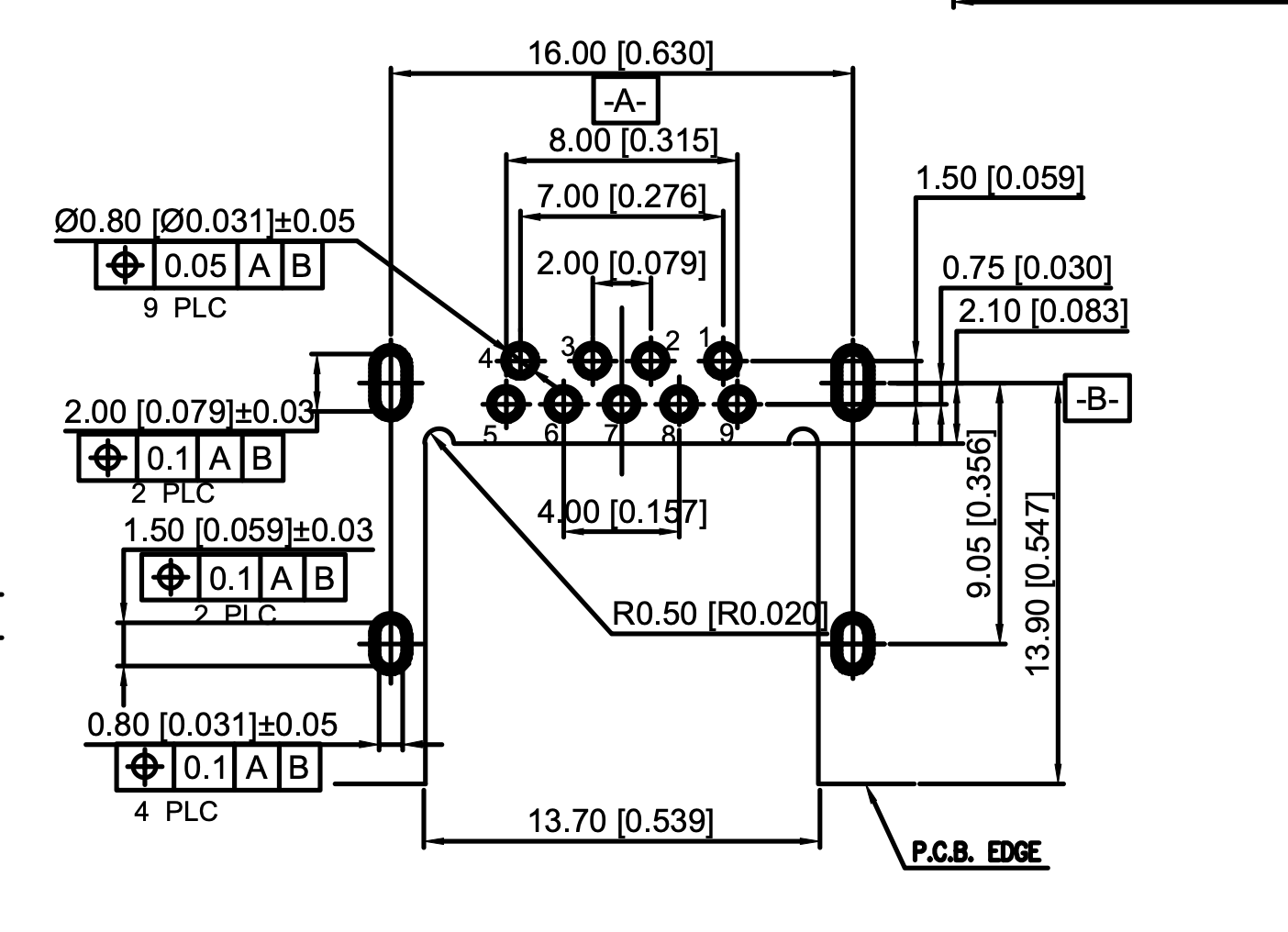

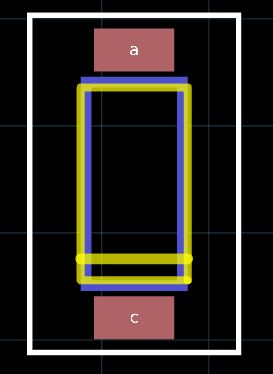

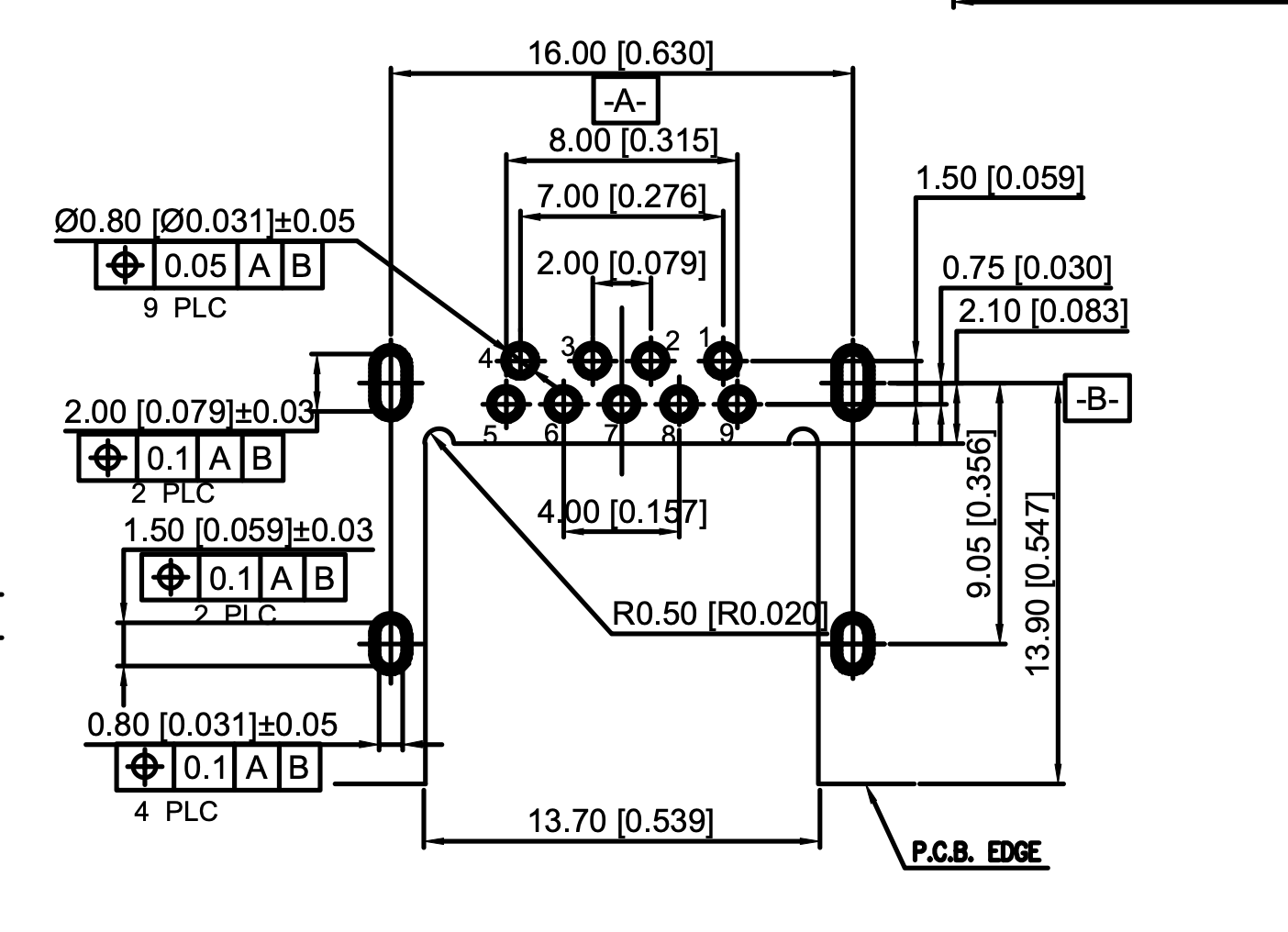

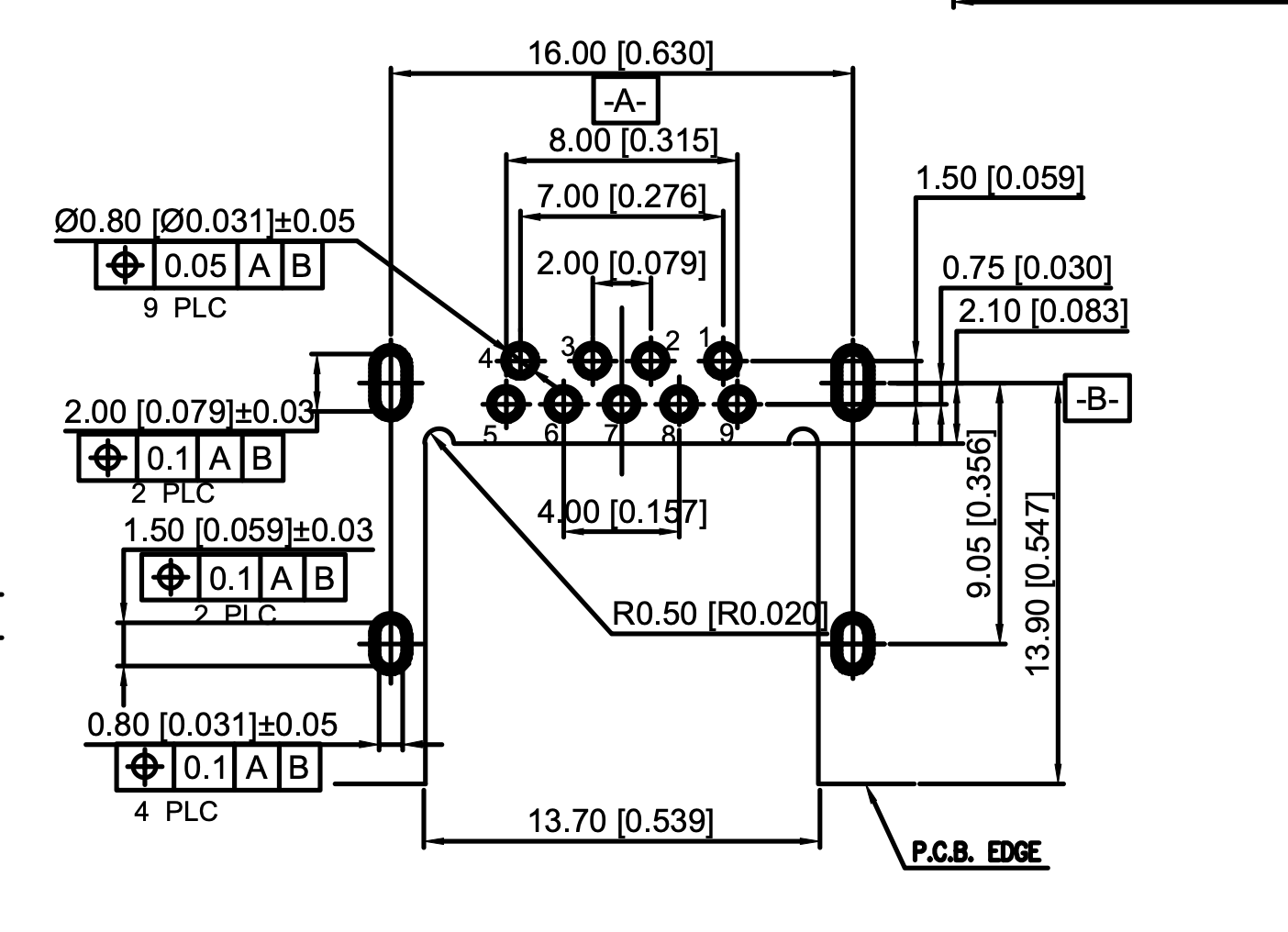

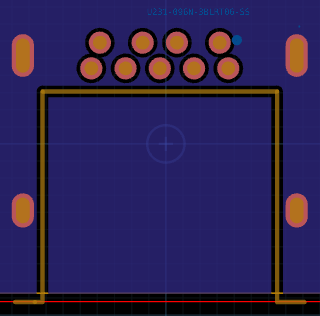

Consider a USB connector part, U231-096N-3BLRT06-SS, Jing Extension of the Electronic Co.

Here is an excerpt from the datasheet:

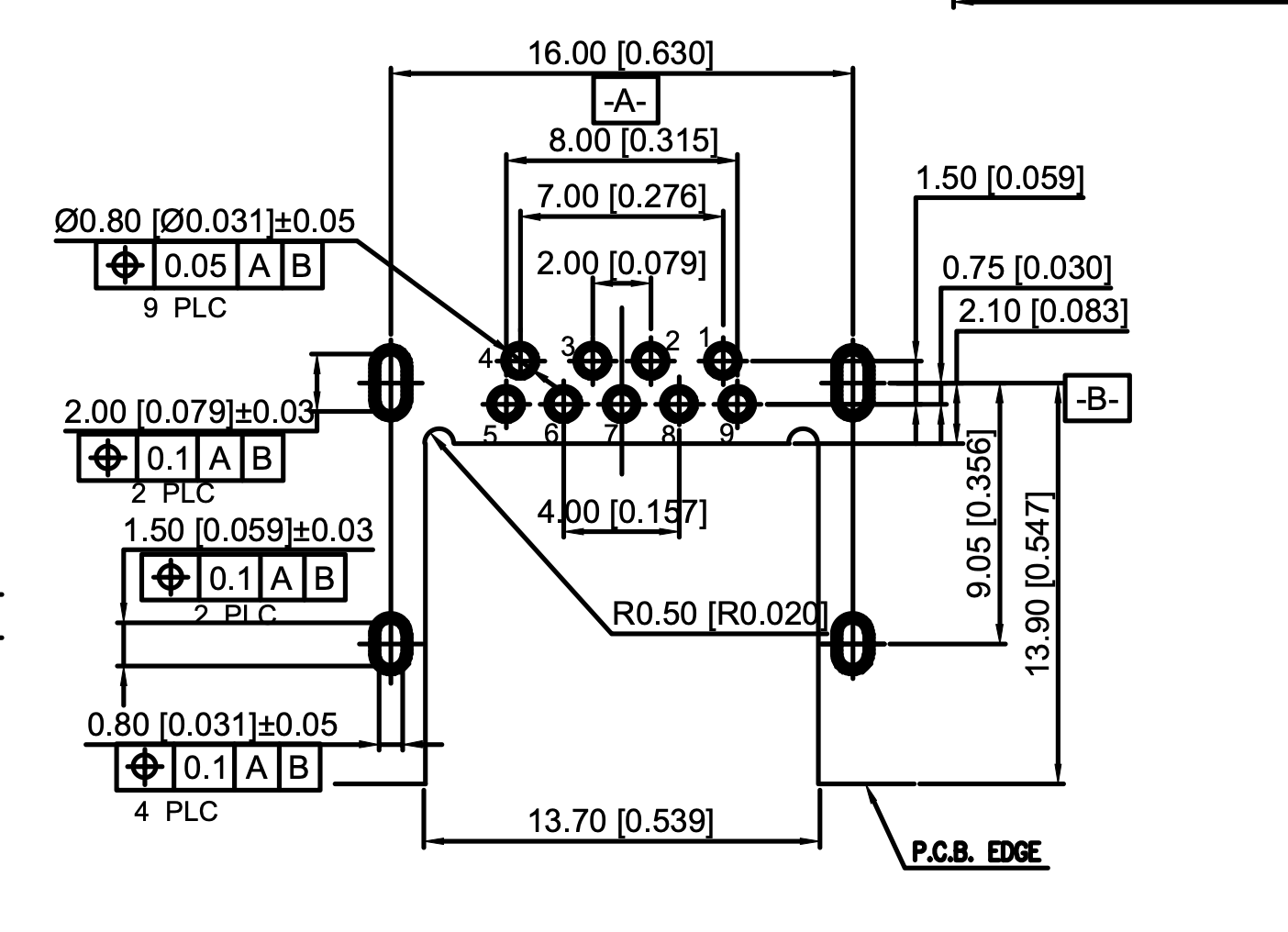

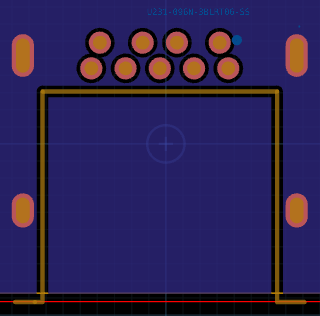

If we draw the cutout with a line, as shown in the datasheet, we get this:

pcb-landpattern USB-conn:

...

layer(Cutout()) = Line(0.254, [Point(-7.300, -7.650), Point(-8.450, -7.650)])

layer(Cutout()) = Polyline(0.254, [

Point(6.850, 4.650)

Point(6.850, -7.650)

Point(8.450, -7.650)])

layer(Cutout()) = Polyline(0.254, [

Point(-6.850, 4.650)

Point(-6.850, -7.650)

Point(-7.300, -7.650)])

layer(Cutout()) = Line(0.254, [Point(-6.850, 4.650), Point(6.850, 4.650)])

The cutout line is in gold color. Notice that the ground layer (blue) copper is present on both sides of the cut line with some margin in between. The routing engine basically thinks that the cutout is just the line. If we were making a slot - that would probably be reasonable. But for this case, we want the hole region between the cutout line and the board edge (red) to be a cutout region.

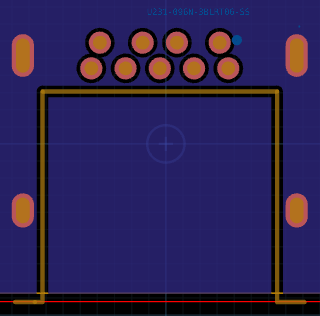

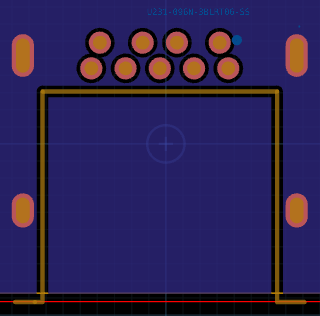

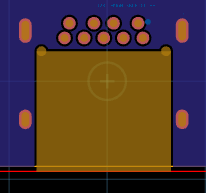

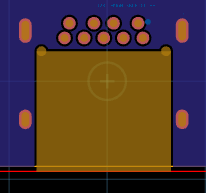

The right way is to use a Rectangle or Polygon solid geometry:

pcb-landpattern USB-conn :

...

layer(Cutout()) = Polygon([

Point(-6.850, 4.650), Point(6.850, 4.650),

Point(6.850, -7.650), Point(-6.850, -7.65),

])

layer(Cutout()) = Circle(Point(-6.85 + 0.5, 4.65), 0.5)

layer(Cutout()) = Circle(Point(6.85 - 0.5, 4.65), 0.5)

Notice that the cutout region fills the entire connector region and the blue ground plane is not present in the cutout region.

Bundle Statements

A pcb-bundle definition groups a set of pins. Bundles can include ports and other bundles. You can connect bundles using a net statement, or use supports and require statements with bundles for automated pin assignment.

For example we can create a bundle for an i2c bus with the following statement:

pcb-bundle i2c:

pin sda

pin scl

Bundles can be parametric and include other bundles. Here is a definition for a bank of lvds pins of variable size:

pcb-bundle diff-pair :

pin N

pin P

pcb-bundle lvds-bank (width:Int) :

port clk : diff-pair

port data : diff-pair[width]

You can make bundles parametric to represent optional pins. Here's an example of a parametric SWD bundle, that can optionally include the SWO pin:

pcb-bundle swd (swo:True|False) :

pin swdio

pin swclk

pin reset

if swo :

pin swo

Statements

Here is the list of all of the statements you can use in a pcb-bundle :

| Statement | Description |

|---|---|

name | Name of the bundle |

description | Description for the bundle |

ports | Creates elements you can connect to |

Name

The name statement is the optional name field of a JITX object. Use it to store a descriptive name as a String. This name will often be used in the UI in place of the object's expression name for better readability.

Signature

name = <String>

This statement is optional. The default value will be the definition's symbol name in case no name statement is found in a definition.

Any string is a valid name value.

Usage

Literal String Names

pcb-component component :

name = "ADM7150"

pcb-module band-pass-filter :

name = "Band-pass filter"

The examples name = "ADM7150" and name = "Band-pass filter" use a String liternal for the name.

Formatted Strings

pcb-pad smd-pad (anchor:Anchor, w:Double, h:Double) :

name = to-string("%_x%_ %_ SMD Pad" % [w,h,anchor])

pcb-landpattern test-lp:

pad p[1] : smd-pad(C, 0.6, 0.7) at loc(x0,y0)

We can also construct strings using formatting routes and parameter arguments for a particular definition. In this example, the constructed smd-pad name property would be 0.6x0.7 C SMD Pad

Description

The description statement is the optional descriptive field of a JITX object. Use it to store a description of the object for human designers reading JITX, and to make the object easier to find via text search. This description also shows up in the UI, such as the design explorer, to provide more insight into particular components and modules in the design.

Signature

description = <String|False>

This statement is optional. The default value will be false in case no description statement is found in a definition.

Any string is a valid description value.

Each JITX definition may have exactly one description statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Examples

; We can use string literals to describe a particular component.

pcb-component analog-devices-ADM7150 :

description = "800 mA Ultralow Noise, High PSRR, RF Linear Regulator"

; We can use string formatting to construct descriptions based on variables

; or arguments to a JITX Definition

pcb-module band-pass-filter (high-cut:Double, low-cut:Double) :

description = to-string(

"Band-pass Filter - Highpass = %_ Hz and Lowpass = %_ Hz." % [high-cut, low-cut]

)

Ports

port is a JITX statement that defines the electrical connection points for a component or module.

The port statement can be used in the following contexts:

Each port statement in any of these contexts is public by default. This means that each port can be accessed externally by using dot notation.

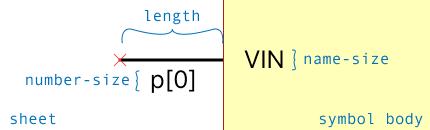

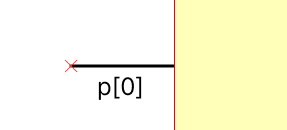

Signature

; Single Port Instance

port <NAME> : <TYPE>

; Array Port Instance

port <NAME> : <TYPE>[<ARRAY:Int|Tuple>]

<NAME>- Symbol name for the port in this context. This name must be unique in the current context.<TYPE>- The type of port to construct. This can be the keywordpinfor a single pin type or any declaredpcb-bundletype.<ARRAY:Int|Tuple>- Optional array initializer argument. This value can be:Int-PortArrayconstructed with lengthARRAY. This array is constructed as a contiguous zero-index array.Tuple-PortArrayconstructed with an explicit set of indexes. This array is not guaranteed to be contiguous.

Watch Out! - There is no space between

<TYPE>and the[opening bracket of the array initializer.

Shortcut Alias

; Single Port - Pin Type

pin <NAME>

The pin name statement is a shortcut for port name : pin

Syntax

There are multiple forms of the port statement to allow for flexible construction of the interface to a particular component. The following sections outline these structures.

Basic Port Declaration

The user has two options when declaring a single pin:

; Single Pin 'a'

port a : pin

; Equivalent to

pin a

The pin a structure is a shorthand version for declaring single pins.

Pin Arrays

To construct a bus of single pins, we use the array constructor:

port contiguous-bus : pin[6]

port non-contiguous-bus : pin[ [2, 5, 6] ]

println(indices(non-contiguous-bus))

; Prints:

; [2 5 6]

The contiguous-bus port is defined as a contiguous array of pins with indices: 0, 1, 2, 3, 4, & 5.

The non-contiguous-bus port is defined an array with explicit indices: 2, 5, & 6. The indices function is a helper function for determining what array indices are available on this port.

Attempting to access a port index that does not exist or is negative will result in an error.

There is no shorthand version for creating PortArray instances with the pin statement.

Bundle Port

A bundle port is a connection point that consolidates multiple individual signals into one entity. The structure of this port is defined by the pcb-bundle type used in its declaration:

pcb-bundle i2c:

pin sda

pin scl

pcb-module mcu:

port data : i2c

In this example, we define the i2c bundle. Notice that this bundle is constructed from same port/pin statements defined above.

The data port is then constructed with the bundle name i2c as the type.

The individual signals of the data port are accessible using dot notation:

pcb-module top-level :

inst U1 : mcu

println(port-type(mcu.data.sda))

; Prints:

; [SinglePin object]

Bundle Array Port

As with the single pin, we can construct port arrays of bundle types:

pcb-bundle i2c:

pin sda

pin scl

pcb-module mcu:

port busses : i2c[3]

In this example, we construct a contiguous array of 3 I2C bus ports. We can access the individual signals of these busses as well:

pcb-module top-level :

inst U1 : mcu

println(port-type(mcu.busses[0].scl))

; Prints:

; [SinglePin object]

Port Types

Each port has a type associated with it. That type can be accessed with the function port-type. This function returns a PortType instance that can be one of the following types:

SinglePin- A port instance of typepinBundle- A port instance of type BundlePortArray- An array of port instances

We would typically use the result of this function with a match statement:

pcb-module amp:

port vout : pin[4]

match(port-type(vout)):

(s:SinglePin): println("Single")

(b:Bundle): println("Bundle")

(a:PortArray): println("Array")

This structure allows a different response depending on the type of port.

The Bundle PortType

The Bundle port type provides the user with access to the type of bundle that was used to construct this port:

pcb-bundle i2c:

pin sda

pin scl

pcb-module mcu:

port bus : i2c

pcb-module top-level:

inst U1 : mcu

match(port-type(U1.bus)):

(b:Bundle):

println("Bundle Type: %_" % [name(b)])

(x): println("Other")

; Prints:

; Bundle Type: i2c

Notice that the b object is a reference to the pcb-bundle i2c definition. This provides a convenient way to check if a given port matches a particular bundle type.

Walking a PortArray

It is often useful to walk a PortArray instance and perform some operation on each of the SinglePin instances of that PortArray. Because PortArray instances can be constructed from either single pins or bundles, they can form arbitrarily complex trees of signals. To work with trees of this nature, recursion is the tool of choice.

Note: This is a more advanced example with recursion. Fear not brave electro-adventurer - These examples will serve you well as you become more comfortable with the JITX Environment.

defn walk-port (f:(JITXObject -> False), obj:JITXObject) -> False :

match(port-type(obj)):

(s:SinglePin): f(obj)

(b:Bundle|PortArray):

for p in pins(obj) do:

walk-port(f, p)

pcb-module top-level:

port bus : i2c[3]

var cnt = 0

for single in bus walk-port :

cnt = cnt + 1

println("Total Pins: %_" % [cnt])

; Prints

; Count: 1

; Count: 2

; Count: 3

; Count: 4

; Count: 5

; Count: 6

The i2c bundle has 2 pins and there are 3 i2c ports in the array which results in 6 total pins.

In this example, we construct a Sequence Operator that will allow us to walk the pins of a port. The structure of a Sequence Operator is:

defn seq-op (func, seq-obj) :

...

Where the seq-obj is a Sequence of objects. The for statement will iterate over the objects in the seq-obj sequence and then call func on each of the objects in the sequence. The value returned by this function can optionally be captured and returned.

In our example, walk-port is a Sequence Operator that doesn't return any result. Notice how walk-port has replaced the do operator that we normally see in a for loop statement.

So where does the func function come from then? The for statement constructs a function from the body of the for statement. In this example, the function effectively becomes:

defn func (x:JITXObject) -> False :

cnt = cnt + 1

Notice that this function is a closure. It is leveraging the top-level context to access the cnt variable defined before the for statement.

A similar construction in Python might look like:

cnt = 0

def func(signal):

global cnt

cnt = cnt + 1

for x in walk-port(bus):

func(x)

Where walk-port would need to be implemented as a generator

in python that constructs a sequence.

Check Statements

Checks are how we check our designs for correctness. We can write arbitrary code to scan through our designs, inspect the data and make sure the circuit will work as designed. The checking functions contain code that generates a well formatted report, that prompts us to enter more data or points out errors in our design.

ocdb/utils/checks has a large set of common checks, and code to apply those automatically checks to a design.

We can also define checks that are specific to a circuit or component. The goal is to create circuit generators that check themselves for correctness, making our design work more reusable.

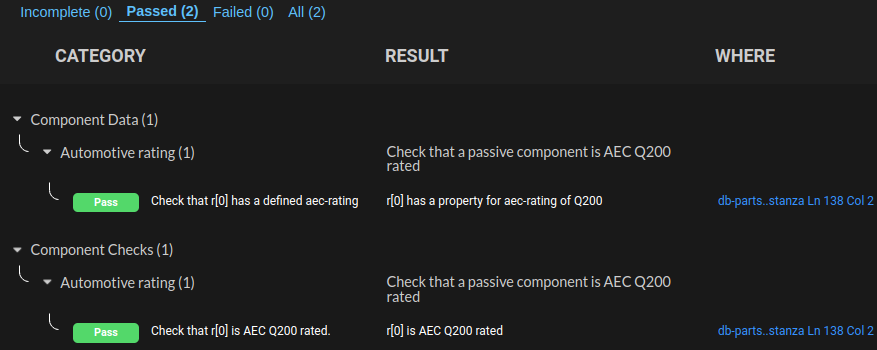

Example check for AEC ratings

pcb-check aec-q200 (component:JITXObject):

#CHECK(

name = "Automotive rating"

description = "Check that a passive component is AEC Q200 rated"

condition = has-property?(component.aec-rating),

category = "Component Data"

subcheck-description = "Check that %_ has a defined aec-rating" % [ref(component)],

pass-message = "%_ has a property for aec-rating of %_" % [ref(component) property(component.aec-rating)],

info-message = "%_ does not have an aec-rating property attached" % [ref(component)],

locators = [instance-definition(component)]

)

#CHECK(

name = "Automotive rating"

description = "Check that a passive component is AEC Q200 rated"

condition = property(component.aec-rating) == "Q200",

category = "Component Checks"

subcheck-description = "Check that %_ is AEC Q200 rated." % [ref(component)],

pass-message = "%_ is AEC Q200 rated" % [ref(component)],

fail-message = "%_ is not AEC Q200 rated. Instead has rating %_." % [ref(component) property(component.aec-rating)],

locators = [instance-definition(component)]

)

pcb-module checked-design :

inst r : chip-resistor(1.0)

check aec-q200(r)

Statements

Here is the list of all of the statements you can use in a pcb-check :

| Statement | Description |

|---|---|

#CHECK | Registers a check to add to report. |

#CHECK

We use #CHECK statements to evaluate conditions in our designs, and then show a Pass Add Info or Fail state.

Syntax

pcb-check aec-q200 (component:JITXObject):

#CHECK(

name = "Automotive rating"

description = "Check that a passive component is AEC Q200 rated"

condition = has-property?(component.aec-rating),

category = "Component Data"

subcheck-description = "Check that %_ has a defined aec-rating" % [ref(component)],

pass-message = "%_ has a property for aec-rating of %_" % [ref(component) property(component.aec-rating)],

info-message = "%_ does not have an aec-rating property attached" % [ref(component)],

locators = [instance-definition(component)]

)

#CHECK(

name = "Automotive rating"

description = "Check that a passive component is AEC Q200 rated"

condition = property(component.aec-rating) == "Q200",

category = "Component Checks"

subcheck-description = "Check that %_ is AEC Q200 rated." % [ref(component)],

pass-message = "%_ is AEC Q200 rated" % [ref(component)],

fail-message = "%_ is not AEC Q200 rated. Instead has rating %_." % [ref(component) property(component.aec-rating)],

locators = [instance-definition(component)]

)

Description

The above #CHECK statements generate this report, when run on a component with instance nae r[0].

name The name of the check

description The top-level description of the check in the report

condition A boolean expression that evaluates to true or false. This condition defines if the check passes, or fails.

category The top-level category to organize this check in the report.

subcheck-description A detailed description of the result of this specific #CHECK

pass-message What should be printed in the report if condition resolves to true

fail-message What should be printed in the report if condition resolves to false and the #CHECK describes a design error. A #CHECK can have a fail-message or a pass-message but not both.

info-message What should be printed in the report if condition resolves to false and the #CHECK describes missing data. A #CHECK can have a fail-message or a pass-message but not both.

locators A list of code locators that help the reader of the report what specific aspect of the design needs attention when the #CHECK fails.

Components

A pcb-component statement defines a model for a single part that can be placed on a board. There are many examples of component definitions to be found in the open-components-database. Components have ports, schematic symbols, a landpattern, and associated metadata.

The primary functions of the pcb-component statement are:

- Provide the sourcing information to include this component in the BOM

- Provide the mapping between schematic symbol pins and land pattern pads.

- Provide the electrical interface to a component and make abstractions where necessary.

- Provide engineering data for signal integrity and other analysis.

Signature

pcb-component comp-name (arg1:Type1, ...) :

name = <String>

description = <String|False>

manufacturer = <String|False>

mpn = <String|False>

datasheet = <String|False>

reference-prefix = <String>

<PORT-1>

...

<PIN-PROP-TABLE-1>

...

<SYMBOL>

<LANDPATTERN>

; Simulation Support

emodel = <MODEL>

; SI Pin Model Definitions

pin-model(<PORT-1>) = PinModel(...)

pin-model(<PORT-1>, <PORT-2>) = PinModel(...)

; Property Definitions

property(self.<PROP-NAME-1>) = <JITXValue>

...

property(self.<PORT-1>.<PROP-NAME>) = <JITXValue>

...

<SUPPORTS-1>

...

no-connect(<PORT-1>)

<EVAL-WHEN-1>

...

The expression name comp-name uniquely identifies this component definition

in the current context.

The argument list (arg1:Type1, ...) is optional and provides a means of

constructing parameterized component definitions.

Required Parameters

<SYMBOL>- The symbol statement defines the schematic symbol representation for this component. There are two primary forms:- Symbol Mapping Form - Explicit Mapping of component ports to symbol pins

- Symbol Unit Form - Allows mapping multiple symbol units to the ports of a component.

- The

assign-symbolutility is a tool for automating this mapping with the help of the pin property table. - Only one

symbolstatement is allowed per component.

<LANDPATTERN>- The landpattern statement defines the land pattern (or footprint) for this component and the mapping from component ports to land pattern pads.- The

assign-landpatternutility is a tool for automating this mapping with the help of the pin property table. - Only one

landpatternstatement is allowed per component.

- The

Optional Parameters

name- This name is used in the Board UI as a more user friendly name. If this string is not provided then thecomp-nameexpression is used as the component's name.description- This string is defining more meta-data for the component.manufacturer- This string defines the manufacturer for this component.mpn- This string defines the manufacturer's part number for this component.datasheet- This string defines the URL to the datasheet for this component.reference-prefix- This string defines the reference designator prefix, for exampleCfor capacitors,Rfor resistors,Qfor transistors, etc. It not provided, this defaults toU.<PORT-1>- A component typically has zero or more port statements.<PIN-PROP-TABLE-1>- A component may have 1 or more pin property tables that provide a convenient way to specify the symbol to landpattern mapping.emodel- The emodel statement allows the user to associate a simulation model with this component. Only one statement of this type is allowed per component definition.pin-model- The pin-model statement is a means of associating a Signal Integrity model with a particular component's ports.property- The property statement allows the user the opportunity to associate data with the component itself or with individual ports of the component.<SUPPORTS-1>- The supports statement allows the user to define pin assignment problems.no-connect- The no-connect statement allows the user to mark a port on a component as not connected to any net and reserving that state as not an error.<EVAL-WHEN-1>- The eval-when statement provides a convenient method to generate checks on a component later in the design run after the circuit's structure has been built.

Usage

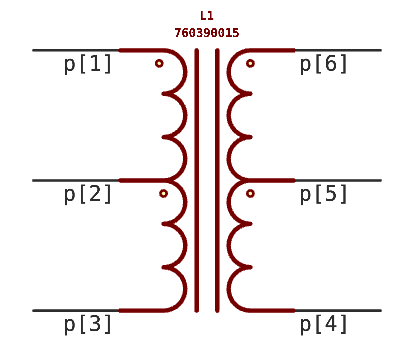

Here is an example definition for an Epson FC-135 crystal oscillator:

pcb-component epson-fc-135 :

name = "32.768kHz Crystal"

description = "CRYSTAL 32.7680KHZ 7PF SMD"

manufacturer = "Epson"

mpn = "FC-135 32.768KA-AG0"

reference-prefix = "Y"

; Port Declarations

port p : pin[[1 2]]

; Symbol to Land Pattern Mapping

val sym = crystal-sym(0)

symbol = sym(p[1] => sym.p[1], p[2] => sym.p[2])

landpattern = xtal-2-3215(p[1] => xtal-2-3215.p[1], p[2] => xtal-2-3215.p[2])

property(self.load-capacitance) = 7.0e-12

property(self.shunt-capacitance) = 1.0e-12

property(self.motional-capacitance) = 3.4e-15

property(self.ESR) = 70.0e3

property(self.frequency) = 32.768e3

property(self.frequency-tolerance) = 20.0e-6

property(self.max-drive-level) = 0.5e-6

It is common to place the manufacturer, mpn, datasheet, and similar labels near the top of a pcb-component definition.

The port declarations define the electrical interface to this component.

The symbol and landpattern statements define the mapping between the symbol, the landpattern, and the electrical interface of this component.

The property statements provide meta-data and characteristics for this device or for any of its ports.

Port Declaration

There are three main ways to declare the ports of a pcb-component.

- Explicit Port Declarations

- Pin Property Table

- Combination of Explicit and Pin Property Table

The epson-fc-135 definition above is an example of "Explicit Port Declarations". With explicit port declarations, we must use the explicit mapping forms of the symbol and landpattern statements.

The Pin Properties Table is a convenience mechanism for mapping the component ports to schematic symbol pins and land-pattern pads. It also simplifies the process of constructing ports.

pcb-component NPN :

pin-properties:

[pin:Ref | pads:Int ...]

[b | 1 ]

[c | 2 ]

[e | 3 ]

assign-symbol(bjt-sym())

assign-landpattern(SOT95P280X100-3N)

Notice that in this example - there are no port statements to explicitly declare the ports b, c, or e. The pin-properties table constructs these ports as SinglePin ports if they are not found at run time.

Combining Explicit & Pin Properties Table

Sometimes is very useful to combine these two approaches. This is especially true when we want the interface to a component to be bundle defined. For example:

pcb-component accelerometer:

port bus : i2c

pin-properties:

[pin:Ref | pads:Int ... | side:Dir ]

[bus.sda | 1 | Left ]

[bus.scl | 2 | Left ]

[VDD | 3 | Right ]

[GND | 4 | Left ]

[ADDR | 5 | Right ]

make-box-symbol()

assign-landpattern(SOT95P280X145-5N)

This example is a bit contrived - but the idea here is that we can forward declare ports that are not of type SinglePin. In this example, bus is a Bundle type port. The properties table can then refer to individual SinglePin ports of the bus port. In this case the i2c bundle only has the sda and scl ports.

Supports & Requires

The pcb-component statement can contain supports statements. These statements provide a means of constructing pin assignment problems.

pcb-component MCU:

pin-properties:

[pin:Ref | pads:Int ... ]

for i in 1 through 16 do:

[ PA[i] | i ]

supports i2c:

i2c.sda => PA[2]

i2c.scl => PA[3]

While supports statements can be used at will in a pcb-component context, the require statement is more restricted. Placing a restrict statement in the body of a pcb-component statement will result in an error:

pcb-component MCU:

pin-properties:

[pin:Ref | pads:Int ... ]

for i in 1 through 16 do:

[ PA[i] | i ]

supports i2c:

i2c.sda => PA[2]

i2c.scl => PA[3]

require bus:i2c from self

The last line of this example will elicit the following error:

Errors occured during parsing:

... Syntax Error: Expression expected here.

The require statement can be used from within a supports statement:

pcb-component MCU:

pin-properties:

[pin:Ref | pads:Int ... ]

for i in 1 through 16 do:

[ PA[i] | i ]

for i in i through 16 do:

supports gpio:

gpio.gpio => PA[i]

supports i2c:

require p1:gpio

require p2:gpio

i2c.sda => p1

i2c.scl => p2

Notice that this creates a cascade of supports and require statements. We call this a Nested supports or require statement. We first create a supports statement for each of the GPIO pins in port PA. Then in the supports i2c: statement, we require two of these GPIO pins and assign them to the pending ports for this supports statement (ie i2c.sda and i2c.scl).

This syntax will not result in a parsing error.

Statements

Here is the list of all of the statements you can use in a pcb-component :

| Statement | Description |

|---|---|

datasheet | URL reference to Datasheet for component |

description | Description for the component |

emodel | EModel for the component |

eval-when | Conditional evaluation of code. |

landpattern | Physical land-pattern/footprint for the component. Also mapped to component ports. |

manufacturer | Manufacturer of the component |

mpn | Manufacturer part number of the component |

name | Name of the component |

no-connect | Set a port as "Not Connected" |

pin-properties | An easy way to map component ports to pins on a landpattern. |

ports | Ports usable when this component is instantiated in a module |

property | Properties of the component or its ports. |

reference-prefix | Start of the reference designator (default is "U"). |

require | Construct Abstract Ports inside supports statements |

supports | Supported peripherals for automated pin solving. |

symbol | Schematic symbol for the component. Mapped to the defined ports. |

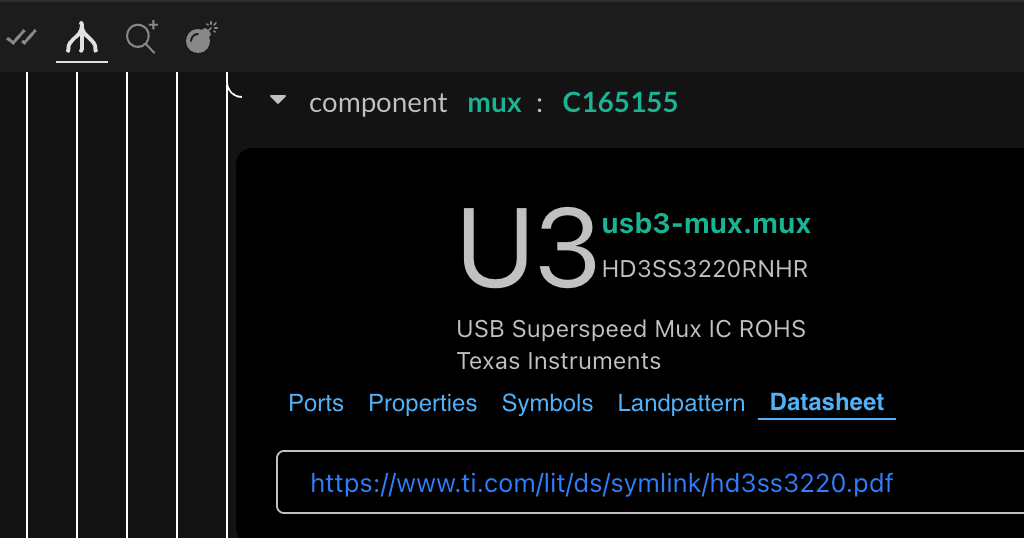

Datasheet

The datasheet statement defines the link to the datasheet of a component.

This statement is valid in the pcb-component context.

Signature

datasheet = <String|False>

This statement is optional. The default value will be false in case no datasheet statement is found in a component definition.

Any string is a valid datasheet value. By convention this is typically a URL.

Each pcb-component may have exactly one datasheet statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Example

pcb-component oscillator:

datasheet = "https://www.analog.com/media/en/technical-documentation/data-sheets/6906fc.pdf"

Here the datasheet links to Analog Devices domain to the LTC6906 component at URL https://www.analog.com/media/en/technical-documentation/data-sheets/6906fc.pdf.

The datasheet URL is used to populate the Design Explorer component properties:

Description

The description statement is the optional descriptive field of a JITX object. Use it to store a description of the object for human designers reading JITX, and to make the object easier to find via text search. This description also shows up in the UI, such as the design explorer, to provide more insight into particular components and modules in the design.

Signature

description = <String|False>

This statement is optional. The default value will be false in case no description statement is found in a definition.

Any string is a valid description value.

Each JITX definition may have exactly one description statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Examples

; We can use string literals to describe a particular component.

pcb-component analog-devices-ADM7150 :

description = "800 mA Ultralow Noise, High PSRR, RF Linear Regulator"

; We can use string formatting to construct descriptions based on variables

; or arguments to a JITX Definition

pcb-module band-pass-filter (high-cut:Double, low-cut:Double) :

description = to-string(

"Band-pass Filter - Highpass = %_ Hz and Lowpass = %_ Hz." % [high-cut, low-cut]

)

EModel

The emodel statement inside a pcb-component associates the component with an electrical model.

Syntax

; define a pcb-component with a resistor EModel

pcb-component my-resisor:

emodel = Resistor(resistance-ohms, tolerance-%, max-power-watts)

Description

An emodel is a simplified model of electrical properties. More complete simulation models can be defined with spice statements (coming soon).

Introspection Command

The emodel? query command returns the electrical model of an instance or a component. The function returns false if there is no electrical model or the argument is not a single component instance.

Different types of EModel's:

; define a resistor EModel

emodel = Resistor(resistance-ohms, tolerance-%, max-power-watts)

; define a capacitor EModel

emodel = Capacitor(capacitance-farads,

tolerance-%,

max-voltage-volts,

polarized?, ; optional boolean

low-esr?, ; optional boolean

temperature-coefficient?, ; optional string, eg "X7R" or "X5R"

dielectric? ; optional) ; optional string, eg "Ceramic, "Tantalum", "Electrolytic"

; define an inductor EModel

emodel = Inductor(inductance-microhenries, tolerance-%, max-current-amps)

; define a diode EModel

emodel Diode(forward-current-amps,

forward-voltage-volts,

max-current-amps,

max-reverse-voltage-volts,

color?, ; optional, for LEDs

luminous-intensity-millicandelas) ; optional, for LEDs

Example Code:

pcb-component cap-component :

emodel = Capacitor(1.0e-007)

pcb-module my-design :

inst cap : cap-component

inst cap-array : cap-component[3]

println("emodel of cap is %_" % [emodel?(cap)])

println("emodel of cap-array[0] is %_" % [emodel?(cap-array[0])])

println("emodel of cap-component is %_" % [emodel?(cap-component)])

The emodel? query returns Capacitor(1.0e-007) for all three calls.

The output is

emodel of cap is Capacitor(1.0e-007)

emodel of cap-array[0] is Capacitor(1.0e-007)

emodel of cap-component is Capacitor(1.0e-007)

The eval-when Statement

When constructing a component or module, there are often times checks we want to write that are dependent on the application. We need to know more about the other circuits we are connected to before we can write the check. To delay the evaluation of these checks until we have the information we need - we use the eval-when statement.

The eval-when statement is valid in the following contexts:

The

eval-whenstatements work in tandem with the run-evals command. Therun-evalsfunction traverses the passed module and orchestrates the running of variouseval-whenblocks. This means foreval-whenstatements in your modules/components to run - you must callrun-evalsat some point after you have completed your design declarations.

Signature

eval-when <CONDITION> :

<STATEMENT-1>

...

- The

<CONDITION>is a predicate (ie, something that evaluates toTrue|False). This condition indicates what data needs to be present in order for thiseval-whento run. - The

<STATEMENT-1>is a list of statements that are valid for the current context. This list of statements is typically called thebodyof theeval-whenstatement. This can be general stanza code or any validpcb-componentorpcb-modulestatements, depending on their respective contexts.

Usage

The eval-when statement is a powerful method of customizing modules for the context in which those modules are instantiated. This method allows us to keep the logic that applies to a particular module or component co-located with the definition of that module or component.

pcb-component LDO :

pin-properties:

[pin:Ref | pads:Int ... ]

[VIN | 1 ]

[GND | 2 ]

[VOUT | 3 ]

...

property(self.VOUT.voltage) = 3.3

property(self.MAX_VIN) = 12.0

property(self.MAX_DROP_OUT) = 0.2

eval-when has-property?(self.VIN.voltage) :

val max-rating = property(self.MAX_VIN)

if self.VIN.voltage > max-rating:

fatal(

"Invalid Input Voltage - %_ exceeds max rating of %_" %

[self.VIN.voltage, max-rating]

)

val min-rating = property(self.VOUT.voltage) + property(self.MAX_DROP_OUT)

if self.VIN.voltage < min-rating :

fatal(

"Invalid Input Voltage - %_ is less than min rating of %_" %

[self.VIN.voltage, min-rating]

)

In this case, we're defining a simple, fixed-voltage LDO regulator. We want to check that the voltage applied to the VIN port is within the expected and allowed range for this component.

For these checks to work - we need to know what voltage is being applied to the VIN port and we don't necessarily know that when the component is instantiated. The eval-when is waiting for the application of a voltage property on the VIN port. Some other entity is going to apply this at the application layer.

Once the voltage property exists on VIN, the statements in the body will execute. In this case we do some minimal checks on the accepted voltage range of VIN.

With Great Power - Comes Great Responsibility

You might notice that this adds some conditional logic to what would otherwise be a purely declarative component or module. This is a concept that doesn't really exist in other legacy CAD tools - ie, you don't typically have to worry about the components mutating.

The safest operations to use inside an eval-when clause are operations that don't modify the physical nature of the PCB:

- Checks - These are typically non-mutating and only read properties or structures.

- BOM Variations - Changing the BOM or any variants is usually OK.

- Adding

no-connect()statements - Adding

property()statements

Operations that are more difficult to use consistently in an eval-when body include:

- Adding

instandnetstatements - Adding concrete ports with the

portstatement. - Adding new abstract ports with the

requirestatement.

There are certainly cases where you might want to use these statements in an eval-when body. These statements are supported and will execute as part of the design run. We suggest proceeding with care and purpose when using these statements.

Land Pattern

The landpattern statement defines the mapping between the component's ports and the pads of the physical land-pattern.

A pcb-component can have only one associated land-pattern.

Signature

; Explicit Mapping Form

landpattern = <LP>(

<PORT-1> => <LP>.<PAD-1>,

<PORT-2> => <LP>.<PAD-2>,

...

)

; Pin Properties Table Form

assign-landpattern(<LP>)

landpattern =statement assigns a landpattern and provides the port to pad mapping explicitly.<LP>- This is a pcb-landpattern definition that will be assigned to the component.<PORT-1>- Refs to individual,SinglePinports of the component<PAD-1>- Refs to individual pads of the<LP>land pattern. Note the use ofdotnotation to specify the pad.- The

=>operator is a mapping operator.

assign-landpattern- This is a utility function that leverages the pin-properties table to automate the construction of the port to pad mapping.- The

<LP>is a pcb-landpattern definition

- The

Usage

The landpattern statement is primarily used in two forms:

- Explicit Mapping Form

- Pin Properties Table Form

Explicit Mapping Form

public pcb-component kelvin-resistor :

manufacturer = "Ohmite"

mpn = "FC4L16R010FER"

port p : pin[[1, 2]]

port sense : diff-pair

val lp = kelvin-lp

landpattern = lp(

self.p[1] => lp.p[1]

self.p[2] => lp.p[2]

self.sense.P => lp.p[3]

self.sense.N => lp.p[4]

)

pcb-landpattern kelvin-lp :

pad p[1] : smd-pad(0.45, 1.2) at loc(0.3625, 0.0)

pad p[2] : smd-pad(0.45, 1.2) at loc(-0.3625, 0.0)

pad p[3] : smd-pad(0.45, 0.4) at loc(0.3625, 1.1)

pad p[4] : smd-pad(0.45, 0.4) at loc(-0.3625, 1.1)

; More Geometry Here

...

When the port names for the component are different from the pad names in the land pattern, we typically need to use the explicit mapping form of the landpattern statement.

This mapping expects the following conditions to be met:

- Each mapping must be from a

SinglePinport to a singlePadon the landpattern. Bundles and PortArrays cannot be mapped with this syntax. - Each component port must have an explicit map. Forgetting a port in the mapping will result in an error.

- Each component port does not necessarily have to be unique. You could have multiple mappings of

GND => p[1],GND => p[2], etc. More on this later. - Each land-pattern pad must be used in only one mapping. If you were to make two mappings with different component ports that both map to

lp.p[1], this will elicit an error.

Pin Properties Table Form

Another way to construct the same component and landpattern mapping would be to use the pin-properties table.

public pcb-component kelvin-resistor :

manufacturer = "Ohmite"

mpn = "FC4L16R010FER"

pin-properties:

[pin:Ref | pads:Ref ...]

for i in 1 through 4 do:

[p[i] | p[i] ]

assign-landpattern(kelvin-lp)

supports diff-pair:

diff-pair.P => self.p[3]

diff-pair.N => self.p[4]

Instead of making an explicit port sense:diff-pair, this version opts to use a supports statement as a means of exposing the differential sense lines of the kelvin resistor. Notice that this version makes no explicit port declarations at all. They are all implicitly defined via the pin-properties table. Upon evaluation, the pin-properties table will create any unknown component ports it finds in the pin column.

In this particular case, the diff-pair supports statement acts more like an interface definition as opposed to a pin-assignment problem. There is only one option for the diff-pair so the solution is trivial. This has the nice benefit of abstracting away what type of component is used to provide the sense interface. For example, it would be easy to swap the kelvin-resistor component with a pcb-module with the same interface but containing a different sensing technique.

One Port to Many Pads

In many electronic components there are multiple pads that map to one functional connection. For example, the ground pin may have 1 or many pads on a component. To support this case, the landpattern statement allows a port ref to be present multiple times. For example in an SMA connector, it is common to have 4 through-hole pads for ground around a center signal pin:

pcb-component SMA :

port launch : pin

port gnd : pin

val lp = SMA-lp

landpattern = lp(

launch => lp.p[1],

for i in 2 through 5 do:

gnd => lp.p[i]

)

val symb = ocdb/utils/symbols/coax-sym

symbol = symb(

launch => symb.sig,

gnd => symb.gnd

)

pcb-landpattern SMA-lp:

pad p[1] : pth-pad(0.75, 1.3) at loc(0.0, 0.0)

pad p[2] : pth-pad(0.8, 1.4) at loc(2.55, 2.55)

pad p[3] : pth-pad(0.8, 1.4) at loc(2.55, -2.55)

pad p[4] : pth-pad(0.8, 1.4) at loc(-2.55, 2.55)

pad p[5] : pth-pad(0.8, 1.4) at loc(-2.55, -2.55)

; More Geometry Here

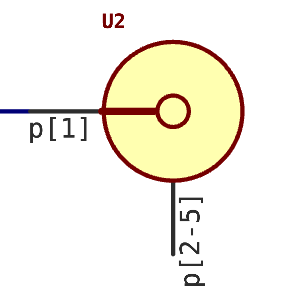

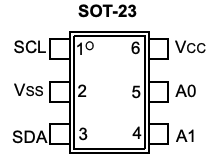

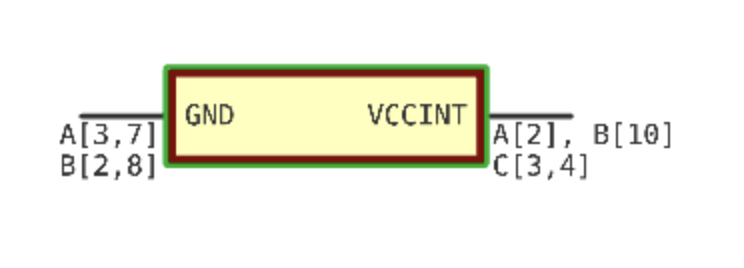

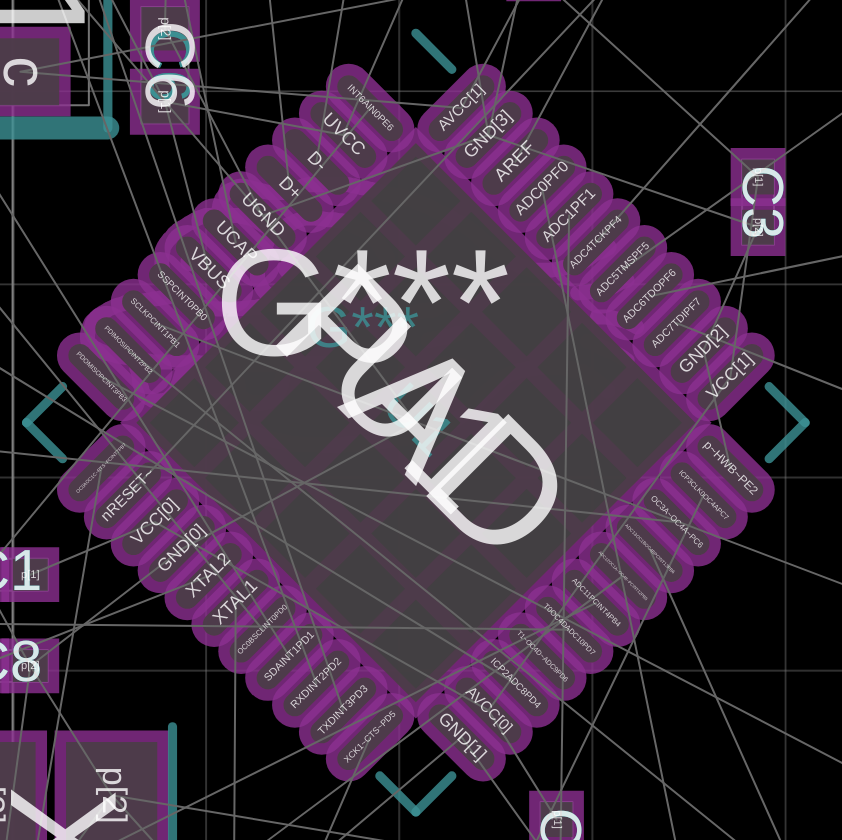

In this example, notice that we use a for-loop to connect the ground pin to the 4 ground through-hole pads of the SMA connector. This has a side effect in the schematic:

Notice that the ground pin on the coax-symb lists its pads as p[2-5]. This is indicating that the ground symbol maps to pins p[2], p[3], p[4], and p[5].

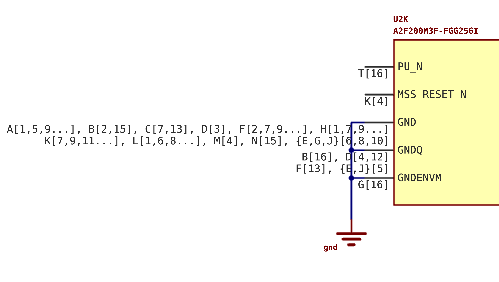

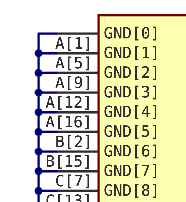

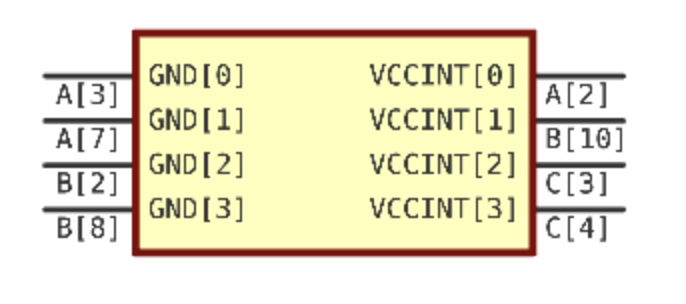

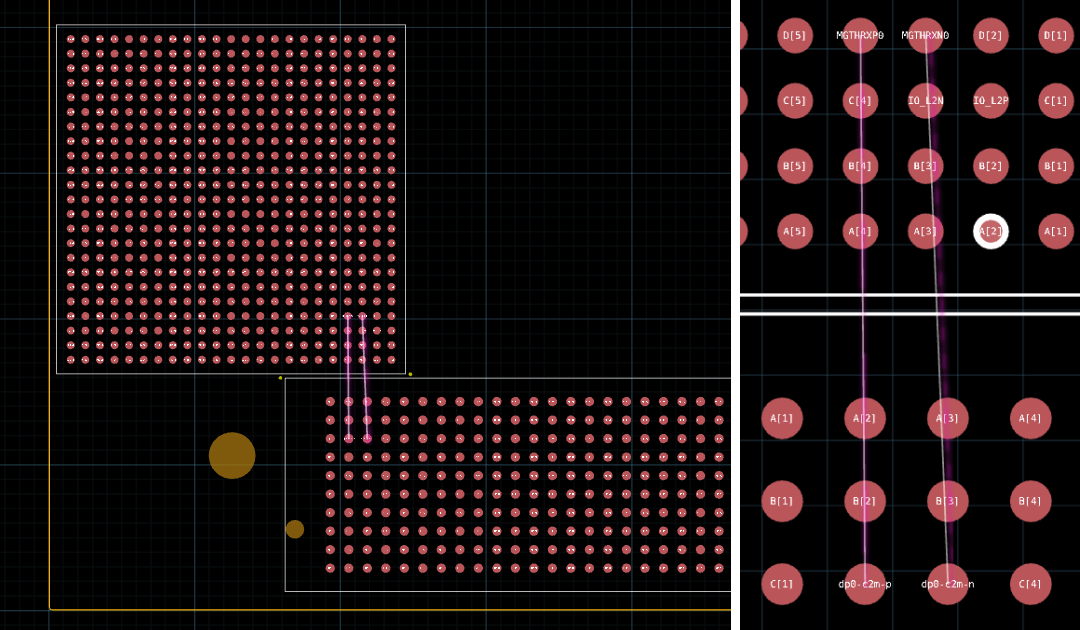

This syntax is very concise for this simple example. Be warned that this syntax doesn't scale as well when considering, for example, a large FPGA with 10s or 100s of ground pins:

In this case, you will likely be better off constructing a PortArray for the GND port and using individual pad mappings:

pcb-component FPGA:

pin-properties:

[pin:Ref | pads:Ref ...]

[GND[0] | A[1] ]

[GND[1] | A[5] ]

[GND[2] | A[9] ]

...

This results in a more readable schematic symbol even if it is a bit larger:

Land Pattern Pads are Internal to Components

The land-pattern and its associated pads are not intended to be exposed outside the component. The components ports are the external interface to a component. Any attempt to net to a pad of a component will result in an error.

Notice that in the above examples, the component port and the landpattern pads use the same ref names. So while this may not be unambiguous - know that the port is what we connect to when constructing the circuit and net list.

Manufacturer

The manufacturer statement defines the manufacturer of a component. It is used to create the bill of materials and to check the sourceability of a pcb-component.

This statement is valid in the pcb-component context.

Signature

manufacturer = <String|False>

This statement is optional. The default value will be false in case no manufacturer statement is found in a component definition.

Any string is a valid manufacturer value.

Each pcb-component may have exactly one manufacturer statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Example

pcb-component TPD3S014DBVR:

manufacturer = "Texas Instruments"

manufacturer = "Texas Instruments" The manufacturer of this component is "Texas Instruments"

MPN

The mpn statement defines the "Manufacturer Part Number" of a component. It is used to create the bill of materials and to check the sourceability of a `pcb-component``.

This statement is valid in the pcb-component context.

Signature

mpn = <String>

This statement is optional. The default value will be false in case no mpn statement is found in a component definition.

Any string is a valid mpn.

Each pcb-component may have exactly one mpn statement. If more than one statement is encountered in a definition, then a DuplicateCStmtError exception will be raised.

Examples

pcb-component usb-iface:

mpn = "TPD3S014DBVR"

pcb-component dip-switch (n-sw:Int = 8)

mpn = to-string("219-%_MSTR" % [n-sw])

In the usb-iface example, mpn = "TPD3S014DBVR" The part number of this component is TPD3S014DBVR

Parametrically constructed components are common pattern. In the dip-switch example, we have an argument n-sw to the component definition. We use this argument value to construct the mpn using string formatting. For the default argument of 8, this results in mpn = "219-8MSTR".

Name

The name statement is the optional name field of a JITX object. Use it to store a descriptive name as a String. This name will often be used in the UI in place of the object's expression name for better readability.

Signature

name = <String>

This statement is optional. The default value will be the definition's symbol name in case no name statement is found in a definition.

Any string is a valid name value.

Usage

Literal String Names

pcb-component component :

name = "ADM7150"

pcb-module band-pass-filter :

name = "Band-pass filter"

The examples name = "ADM7150" and name = "Band-pass filter" use a String liternal for the name.

Formatted Strings

pcb-pad smd-pad (anchor:Anchor, w:Double, h:Double) :

name = to-string("%_x%_ %_ SMD Pad" % [w,h,anchor])

pcb-landpattern test-lp:

pad p[1] : smd-pad(C, 0.6, 0.7) at loc(x0,y0)

We can also construct strings using formatting routes and parameter arguments for a particular definition. In this example, the constructed smd-pad name property would be 0.6x0.7 C SMD Pad

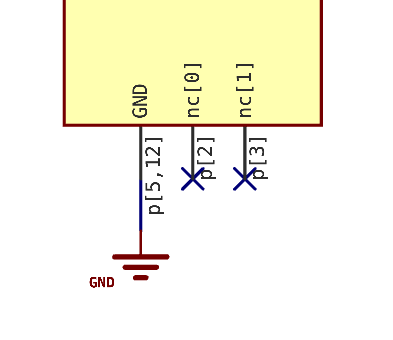

No Connect Statement

The no-connect() statement is a tool for marking a port on a component or module as "Not Connected". This is an indication to the JITX runtime that this port can be left floating without any ill-effect.

This statement can be used from the following contexts:

Signature

no-connect(<PORT>)

<PORT>- The argument to this statement is expected to be aSinglePinport from apcb-componentdefinition or instance.

Usage

The no-connect() statement is typically used to mark individual pins as intentionally not connected:

public pcb-component component :

name = "XDCR_LIS3DHTR"

manufacturer = "STMicroelectronics"

mpn = "LIS3DHTR"

pin-properties :

[pin:Ref | pads:Int ... | side:Dir]

[CS | 8 | Left]

[GND | 5, 12 | Down]

...

[nc[0] | 2 | Down]

[nc[1] | 3 | Down]

[VDD-IO | 1 | Up]

make-box-symbol()

assign-landpattern(xdcr-lis3dhtr)

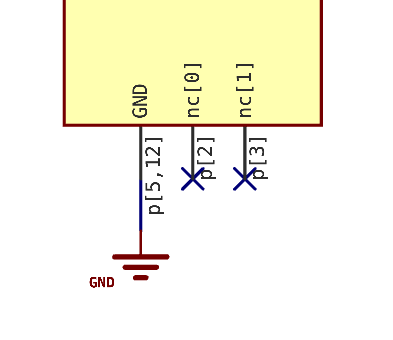

for i in indices(self.nc) do:

no-connect(self.nc[i])

Here the LIS3DHTR has two "NC" pins, pin 2 and 3. This component defines these pins in a PortArray of length 2. The for-loop at the end uses the indices command to loop over all the NC pins.

Notice - that we did not pass self.nc, the PortArray, directly to the no-connect statement. This would elicit an error.

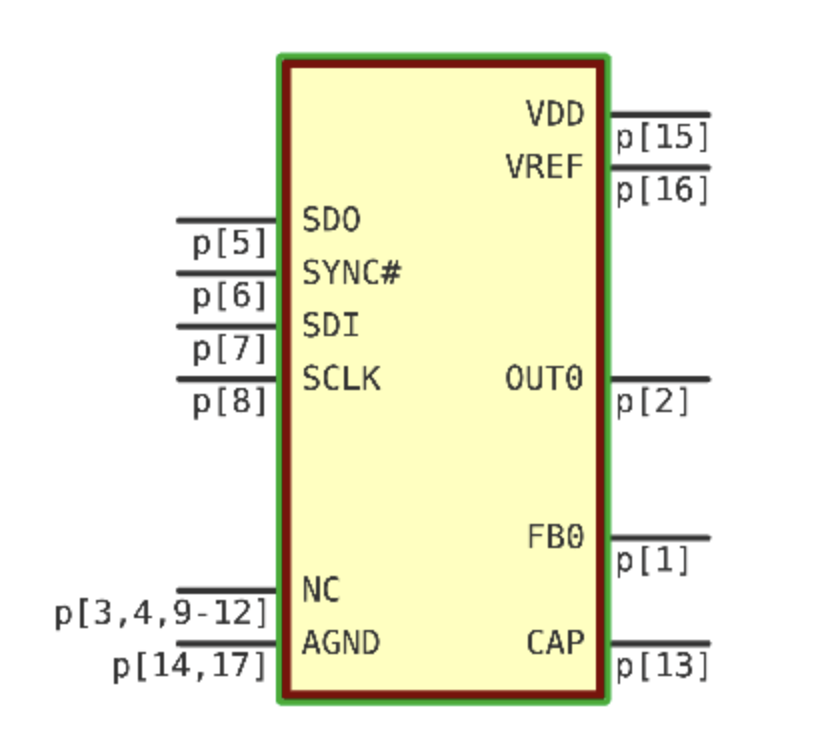

When we view this component in the schematic, we see:

Notice the X over the two NC pins. This is the "No Connect" representation in the schematic.

Usage from pcb-module

When using this statement from a module, we must use the no-connect() statement on one of the ports of the instantiated components in the module. It is an error to apply the no-connect() statement to one of a module's ports.

public pcb-module module :

public inst acc : ocdb/components/st-microelectronics/LIS3DH/component

...

for i in indices(acc.nc) do:

no-connect(acc.nc[i])

Note that duplicate no-connect() statements on a component's port will not throw an error.

If you attempt to use the no-connect statement on a module's port:

pcb-module bad-module:

port unused : pin

no-connect(self.unused)

This will throw an exception:

Uncaught Exception: Tried to get type with an invalid definition.

Testing for "No Connect" Status

The no-connect? command can be used to interrogate a component and determine the "No Connect" status of its pins.

Pin Properties